- #1

perplexabot

Gold Member

- 329

- 5

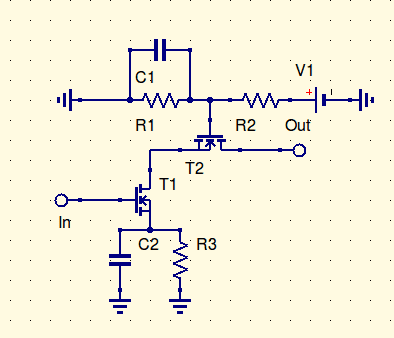

Hello all. I have been looking into RF amps. I have come across the following cascode amp (from ARRL handbook 2014, p 12.10, FIG. 12.11. Thanks to Baluncore for the great reference). Here is a simplified version made with Qucs:

My questions are regarding the capacitors, C1 and C2. Why are they there?

I know that if we were to have only a common source (CS) amplifier the bypass capacitor C2 will provide a larger gain for the small signal required. But this is not the case here, if I am not mistaken, in a cascode configuration, the CS phase does not provide amplification, it provides high input impedance, right? If yes, then why do we care about the small signal gain at that point. Is it not the common gate stage that provides amplification?

I have no idea why C1 is there! I know R1 and R2 set up the Voltage bias at T2, I also know that for small signal, the gate will look like a ground, what is the point of C1?

Thank you.

My questions are regarding the capacitors, C1 and C2. Why are they there?

I know that if we were to have only a common source (CS) amplifier the bypass capacitor C2 will provide a larger gain for the small signal required. But this is not the case here, if I am not mistaken, in a cascode configuration, the CS phase does not provide amplification, it provides high input impedance, right? If yes, then why do we care about the small signal gain at that point. Is it not the common gate stage that provides amplification?

I have no idea why C1 is there! I know R1 and R2 set up the Voltage bias at T2, I also know that for small signal, the gate will look like a ground, what is the point of C1?

Thank you.