- #1

reddvoid

- 119

- 1

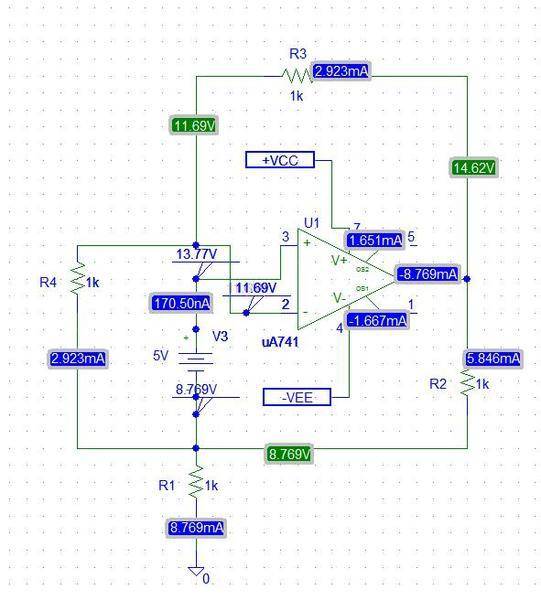

This is the snap shot i took from Pspice simulation

I have a doubt here

***why is voltage at non inverting terminal is 13.77V even though i connected 5V dc source to it and why the voltages at inverting and non inverting terminals are not almost same ( which we consider while solving opamp circuits)

thank you .

I have a doubt here

***why is voltage at non inverting terminal is 13.77V even though i connected 5V dc source to it and why the voltages at inverting and non inverting terminals are not almost same ( which we consider while solving opamp circuits)

thank you .