- #1

saad87

- 85

- 0

I'm designing a 4-layer board with a couple of CPLDs and a uC. The top and bottom layer are for signals and the 2nd layer is ground and the 3rd layer is 3.3V.

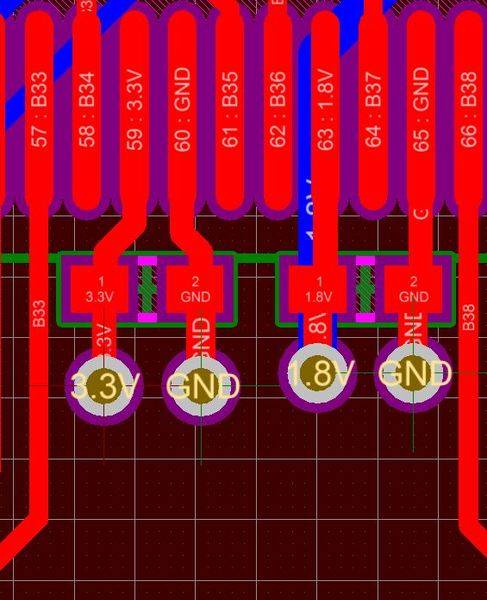

I'm placing a 0.1uF X7R Ceramic cap in 0402 package on every Vcc/Gnd pair. The thing that confuses me is that I've seen several ways in which they are placed. I've placed them in the most obvious way, as shown below:

My question is: is there another arrangement that is more effective? Someone I know recommended placing the power/ground vias between the capacitor and the IC pins. Is that more effective?

Would appreciate some thoughts.

I'm placing a 0.1uF X7R Ceramic cap in 0402 package on every Vcc/Gnd pair. The thing that confuses me is that I've seen several ways in which they are placed. I've placed them in the most obvious way, as shown below:

My question is: is there another arrangement that is more effective? Someone I know recommended placing the power/ground vias between the capacitor and the IC pins. Is that more effective?

Would appreciate some thoughts.