- #1

jaus tail

- 615

- 48

- TL;DR Summary

- I'm struggling to understand how PLL works once the frequency is locked.

From reference:

https://www.elprocus.com/phase-locked-loop-operating-principle-and-applications/

It says that the PD produces an output that is DC level proportional to (Fi - Fo) (I think it has typo. It should be '-' but they've printed '+').

Then the low pass filter removes the high frequency noise and then we give this voltage difference to a VCO to get output frequency proportional to the phase difference.

But then what?

Suppose Fi is 50 Hz. Initially Fo is 0Hz. So output of phase detector is a signal proportional to Fi - Fo which is 50 Hz. So the VCO will produce an output which is proportional to (50 Hz - 0 Hz) = 50 Hz.

Then this becomes Fo = 50 Hz. So now Fi - Fo becomes 50 - 50 = 0Hz. So VCO will get 0Hz and will produce output proportional 0 Hz?As quoted in the website:

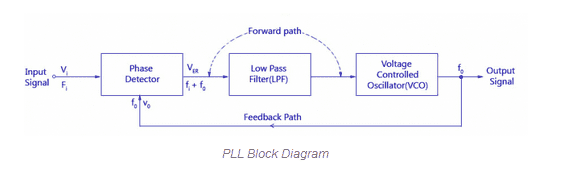

Block Diagram And Working Principle Of PLL

The phase locked loop consists of a phase detector, a voltage control oscillator and, in between them, a low pass filter is fixed. The input signal ‘Vi’ with an input frequency ‘Fi’ is conceded by a phase detector. Basically the phase detector is a comparator which compares the input frequency fi through the feedback frequency fo. The output of the phase detector is (fi+fo) which is a DC voltage. The out of the phase detector, i.e., DC voltage is input to the low pass filter (LPF); it removes the high frequency noise and produces a steady DC level, i.e., Fi-Fo. The Vf is also a dynamic characteristic of the PLL.

The output of the low pass filter, i.e., DC level is passed on to the VCO. The input signal is directly proportional to the output frequency of the VCO (fo). The input and output frequencies are compared and adjusted through the feedback loop until the output frequency is equal to the input frequency. Hence, the PLL works like free running, capture, and phase lock.

When there is no input voltage applied, then it is said to be as a free running stage. As soon as the input frequency applied to the VOC changes and produces an output frequency for comparison, it is called as capture stage. The below figure shows the block diagram of the PLL.

Phase Locked Loop Detector

The phase locked loop detector compares the input frequency and the output frequency of the VCO to produces a DC voltage which is directly proportional to the phase distinction of the two frequencies.

https://www.elprocus.com/phase-locked-loop-operating-principle-and-applications/

It says that the PD produces an output that is DC level proportional to (Fi - Fo) (I think it has typo. It should be '-' but they've printed '+').

Then the low pass filter removes the high frequency noise and then we give this voltage difference to a VCO to get output frequency proportional to the phase difference.

But then what?

Suppose Fi is 50 Hz. Initially Fo is 0Hz. So output of phase detector is a signal proportional to Fi - Fo which is 50 Hz. So the VCO will produce an output which is proportional to (50 Hz - 0 Hz) = 50 Hz.

Then this becomes Fo = 50 Hz. So now Fi - Fo becomes 50 - 50 = 0Hz. So VCO will get 0Hz and will produce output proportional 0 Hz?As quoted in the website:

Block Diagram And Working Principle Of PLL

The phase locked loop consists of a phase detector, a voltage control oscillator and, in between them, a low pass filter is fixed. The input signal ‘Vi’ with an input frequency ‘Fi’ is conceded by a phase detector. Basically the phase detector is a comparator which compares the input frequency fi through the feedback frequency fo. The output of the phase detector is (fi+fo) which is a DC voltage. The out of the phase detector, i.e., DC voltage is input to the low pass filter (LPF); it removes the high frequency noise and produces a steady DC level, i.e., Fi-Fo. The Vf is also a dynamic characteristic of the PLL.

The output of the low pass filter, i.e., DC level is passed on to the VCO. The input signal is directly proportional to the output frequency of the VCO (fo). The input and output frequencies are compared and adjusted through the feedback loop until the output frequency is equal to the input frequency. Hence, the PLL works like free running, capture, and phase lock.

When there is no input voltage applied, then it is said to be as a free running stage. As soon as the input frequency applied to the VOC changes and produces an output frequency for comparison, it is called as capture stage. The below figure shows the block diagram of the PLL.

Phase Locked Loop Detector

The phase locked loop detector compares the input frequency and the output frequency of the VCO to produces a DC voltage which is directly proportional to the phase distinction of the two frequencies.