SUMMARY

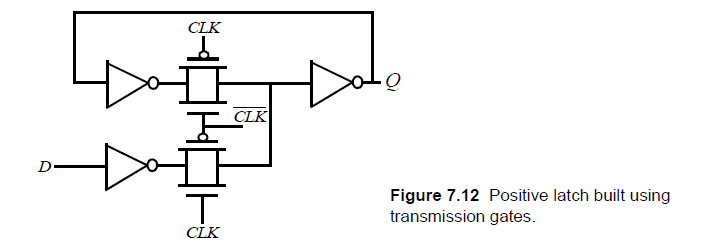

The discussion centers on the use of three inverters in a D latch circuit utilizing transmission gates, as described in "Digital Integrated Circuits" by Jan M. Rabaey. The inverters serve multiple purposes: the lower inverter acts as an input buffer amplifier, while the upper two inverters create a positive feedback loop that retains the last digital output state. This configuration functions as a sample and hold circuit, ensuring signal integrity by compensating for potential voltage drops, thereby maintaining logic levels in digital memory applications.

PREREQUISITES

- Understanding of D latch circuits

- Familiarity with transmission gates

- Knowledge of inverter functionality in digital circuits

- Basic concepts of digital memory elements

NEXT STEPS

- Study the operation of D latches and their applications in digital circuits

- Explore the role of transmission gates in CMOS technology

- Investigate the impact of voltage levels on digital logic states

- Learn about flip-flops and their use as memory elements in digital systems

USEFUL FOR

Electrical engineers, digital circuit designers, and students studying integrated circuit design will benefit from this discussion, particularly those interested in memory elements and signal integrity in digital systems.