Discussion Overview

The discussion revolves around troubleshooting a high-speed synchronous N-channel MOSFET driver circuit, specifically the LTC4449, in a setup involving a 24V switching voltage from a 600W SMPS. Participants are exploring issues related to the gate drive of the top MOSFET, with a focus on the boost circuitry and the appropriate MOSFET selection.

Discussion Character

- Technical explanation

- Debate/contested

- Experimental/applied

Main Points Raised

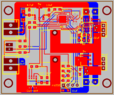

- One participant describes the circuit design and expresses concern that the gate drive for the top MOSFET is not functioning correctly, suspecting an issue with the boost circuitry.

- Another participant questions whether the MOSFET is turning on properly with only 5 volts of gate drive and asks for the specific model of the MOSFET being used.

- Concerns are raised about the measurement of the boost pin voltage, with suggestions to verify the circuit layout and check for potential issues like wrong traces or incorrect component values.

- Participants discuss the implications of using different MOSFETs, noting that the IRF3007PBF may not turn on adequately with a 5V gate signal compared to the IRF7468.

- Suggestions are made to consider alternative MOSFETs with lower gate threshold voltages and to verify the specifications against the datasheets.

- One participant proposes testing with a different power supply module to improve the Vcc stability, while another mentions the importance of bypass capacitors and layout considerations.

- There is a discussion about the boost capacitor's role in providing the necessary voltage for the high-side MOSFET gate drive, with clarification on how it operates in relation to the switching output.

- Frustration is expressed by a participant who has repeatedly attempted to resolve the issue without success, leading to a redesign of the PCB to accommodate a different gate driver.

- Clarifications are provided regarding the maximum voltage specifications for the new gate driver and the implications for the MOSFET operation.

Areas of Agreement / Disagreement

Participants have not reached a consensus on the root cause of the high-side gate signal issue. Multiple competing views exist regarding the appropriate MOSFET selection and the effectiveness of the current circuit design.

Contextual Notes

Participants note potential limitations in the circuit design, including the choice of the linear regulator for Vcc and the need for careful consideration of component specifications. There are unresolved questions about the impact of the boost capacitor and the overall circuit layout.

Who May Find This Useful

Individuals working on high-speed MOSFET driver circuits, those troubleshooting similar power electronics designs, and engineers interested in gate drive strategies for synchronous switching applications may find this discussion relevant.