janor

- 3

- 0

Hi

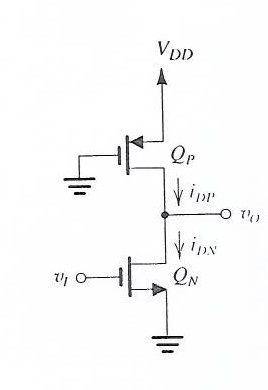

in the Pseudo NMOS inverter below

I don't understand how Qp acts as an active load, what I understand is that with this configuration Qp's Vgs is -5V which means that this transistor is always on (short circuit), now if the input to the circuit is low this means that Qn is off but Qp is on so the output will be high, but if the input is high this means that both Qn & Qp are on, now how come the output will be low? Shouldn't it be floating?

and I tried a simulation on Multisim and the results was as I expected, when the input was low the output was 5V, and when the input was high the output was 4.6V.

in the Pseudo NMOS inverter below

I don't understand how Qp acts as an active load, what I understand is that with this configuration Qp's Vgs is -5V which means that this transistor is always on (short circuit), now if the input to the circuit is low this means that Qn is off but Qp is on so the output will be high, but if the input is high this means that both Qn & Qp are on, now how come the output will be low? Shouldn't it be floating?

and I tried a simulation on Multisim and the results was as I expected, when the input was low the output was 5V, and when the input was high the output was 4.6V.