Discussion Overview

The discussion revolves around the purpose and function of three inverters in a D latch circuit using transmission gates, as presented in a textbook on digital integrated circuits. Participants explore the implications of buffering, feedback, and voltage levels in the context of digital memory elements.

Discussion Character

- Technical explanation

- Conceptual clarification

- Debate/contested

Main Points Raised

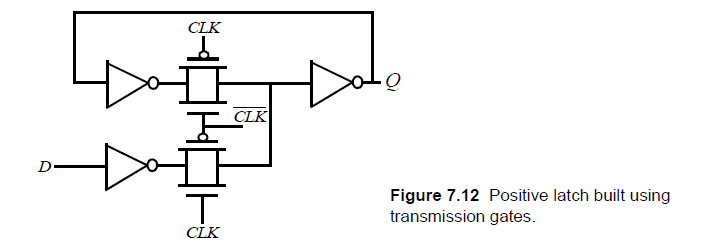

- One participant questions the necessity of the three inverters, noting that their purpose is not explained in the book or found in online resources.

- Another participant suggests that inverters are generally used to buffer inputs and outputs to achieve high input impedance and low output impedance.

- A different participant explains that two inversions can create a non-inverting amplifier and describes the function of the lower inverter as an input buffer amplifier, while the upper two inverters provide positive feedback for digital memory.

- One participant challenges the need for inverters, arguing that two inverters in series produce the same output as the input, questioning their utility.

- Another participant elaborates that two inverters can create a flip-flop, which serves as a memory element.

- One participant proposes that inverters may compensate for voltage drops, ensuring that the output remains within logic levels over time.

Areas of Agreement / Disagreement

Participants express differing views on the necessity and function of the inverters, with no consensus reached on their overall purpose in the circuit.

Contextual Notes

Participants highlight various assumptions about buffering, feedback, and voltage levels, but these remain unresolved within the discussion.