sparkle123

- 172

- 0

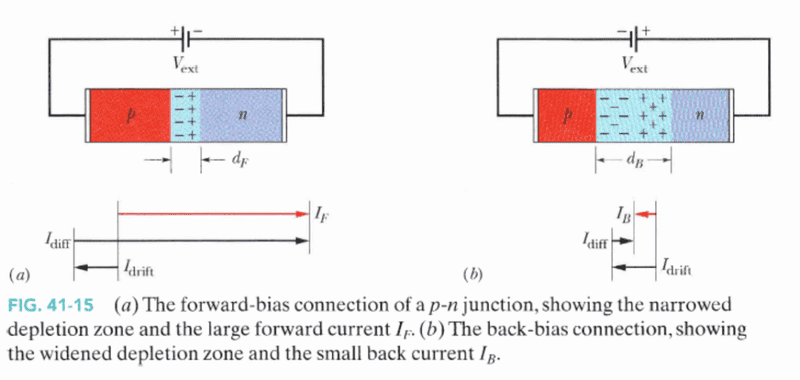

For p-n junctions (connected as a junction rectifier), the forward-bias connection (battery's positive terminal connected at the p side) results in a narrowed depletion zone, because: the p side becomes more positive and the n side becomes more negative, thus decreasing the height of the potential barrier

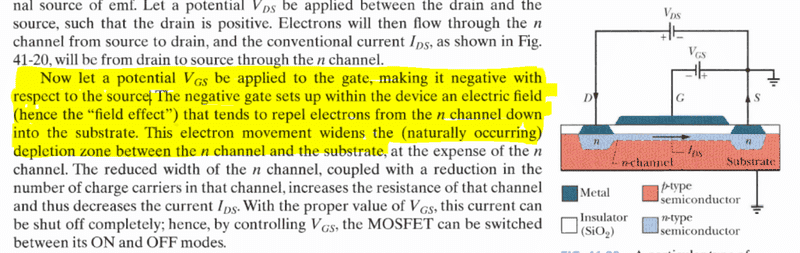

So why in transistors, does the negative gate which repel electrons from the n channel down into the substrate widen the depletion zone, instead of narrowing it, as in p-n junctions?

Thank you very much! I hope my question is adequately clear :)

So why in transistors, does the negative gate which repel electrons from the n channel down into the substrate widen the depletion zone, instead of narrowing it, as in p-n junctions?

Thank you very much! I hope my question is adequately clear :)

Last edited: