jaus tail

- 613

- 48

- Homework Statement

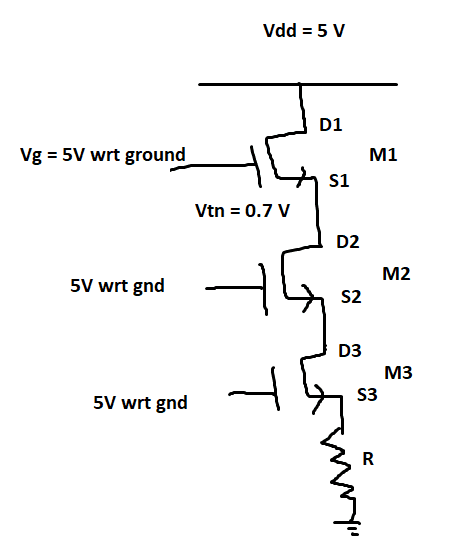

- When three n type mosfets are stacked, what will be potential across V(ds)3 where:

DS1 is drain source of 1st mosfet. Drain is connected to Vdd. Source is connected to drain of second mosfet. Source of second mosfet is connected to third mosfet. Source of third mosfet is connected to resistance that is grounded

Vdd --> Vd1s1 --> Vd2s2 --> Vd3s3 --> R --> Ground

- Relevant Equations

- Mosfet turns on when Vgs > Vtn and Vds > (Vgs - Vtn)

Here's the circuut:

Vtn is 0.7 V. So Vs1 (wrt ground) cannot be more than 4.3 V else M1 won't turn on.

Likewise Vs2 and Vs3 (wrt ground) cannot be more than 4.3 V else M2 won't turn on.

So Vs3 = 4.3 V. Even voltage across final resistance is 4.3 V

Assume there's no drop across Mosfet.

But I'm not sure. Will the drop of 0.7 be accumulated. Like Vs3 would be Vdd - 3 times Vtn?

Will Vs3 (wrt ground) be 4.3 V or (5-3 times 0.7) = 2.9 V

The 2 scenarios for this question are:

1) All mosfets are in saturation mode

2) The mosfets can be in linear mode

Vtn is 0.7 V. So Vs1 (wrt ground) cannot be more than 4.3 V else M1 won't turn on.

Likewise Vs2 and Vs3 (wrt ground) cannot be more than 4.3 V else M2 won't turn on.

So Vs3 = 4.3 V. Even voltage across final resistance is 4.3 V

Assume there's no drop across Mosfet.

But I'm not sure. Will the drop of 0.7 be accumulated. Like Vs3 would be Vdd - 3 times Vtn?

Will Vs3 (wrt ground) be 4.3 V or (5-3 times 0.7) = 2.9 V

The 2 scenarios for this question are:

1) All mosfets are in saturation mode

2) The mosfets can be in linear mode