- #1

CoolDude420

- 198

- 8

- Homework Statement

- N/A

- Relevant Equations

- N/A

I have a question relating DAC architectures. The guts of the question are really to do with capacitors and charge. I want to see if my understanding is correct. This is not a homework question or anything, just thinking about how the circuit interacts.

Setup:

Consider the following setup:

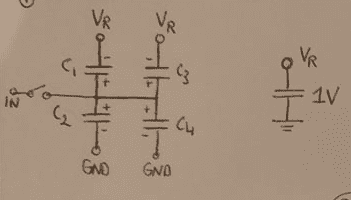

Capacitors C1, C2, C3, C4 where C1 = C2 = 32fF and C3 = C4 = 16fF. All the capacitors in the bank have their top/positive plate connected together. The bottom plate of C1 and C3 is connected to a reference capacitor which is charged to 1V initially (Vr node). The bottom plate of C2 and C4 is connected to GND. There is also an input switch used to sample a voltage onto the top plates of each capacitor.

Step 1 - Sampling:

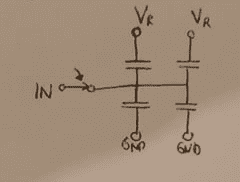

The input switch is closed and the top plates of the capacitors now move with the input voltage (let's say some sinusoid)

Step 2 - Stop Sampling:

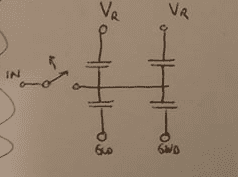

We now open the input switch and a voltage (some voltage of the sinusoid) is sampled on the top plates of each capacitor. Let's call this voltage Vip

Step 3 - Switching:

Here come's the tricky part. Let us now switch the bottom plate of capacitor C2 from GND to Vr.

Here is my understanding of what happens now:

My guess is that:

Setup:

Consider the following setup:

Capacitors C1, C2, C3, C4 where C1 = C2 = 32fF and C3 = C4 = 16fF. All the capacitors in the bank have their top/positive plate connected together. The bottom plate of C1 and C3 is connected to a reference capacitor which is charged to 1V initially (Vr node). The bottom plate of C2 and C4 is connected to GND. There is also an input switch used to sample a voltage onto the top plates of each capacitor.

Step 1 - Sampling:

The input switch is closed and the top plates of the capacitors now move with the input voltage (let's say some sinusoid)

Step 2 - Stop Sampling:

We now open the input switch and a voltage (some voltage of the sinusoid) is sampled on the top plates of each capacitor. Let's call this voltage Vip

Step 3 - Switching:

Here come's the tricky part. Let us now switch the bottom plate of capacitor C2 from GND to Vr.

Here is my understanding of what happens now:

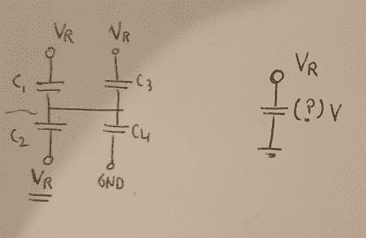

- C2 bottom plate goes from GND to Vr

- To ensure that the voltage/hence charge on C2 remains constant, the top plate of C2 must move to Vip + Vr. Just like in a Dickson charge-pump.

- Since the top plate of C2 is at Vip + Vr, but the top plates of C1, C3, C4 were still at Vip, charge redistribution occurs.

- As part of the charge redistribution process, current (positive charge) flows from the top plate of C2 to the top plates of C1, C3 and C4. The voltage at the common node of all capacitors settles at a steady-state voltage somewhere near Vip + 0.5Vr (I know it can be calculated.)

My guess is that:

- During the charge redistribution process, positive charge had to leave the top plate of C2 to equalise the potential with other capacitors.

- Since +Q (positive charge on positive plate) decreased on C2, then -Q (negative charge on negative plate) must also decrease.

- Thus, electrons flow to the Vr capacitor, thus current leaves Vr capacitor and hence voltage on Vr decreases!

- During the charge redistributon process, the positive charge (+Q) gained on the top plates of C1, C3, C4 means that (-Q) charge on bottom plates of C1, C3, and C4 must increase.

- Thus, electrons flow to the bottom plates of C1, C3, C4 from the reference capacitor, hence current flows to the reference capacitor. Thus, the reference capacitor voltage Vr increases!