- #1

fonz

- 151

- 5

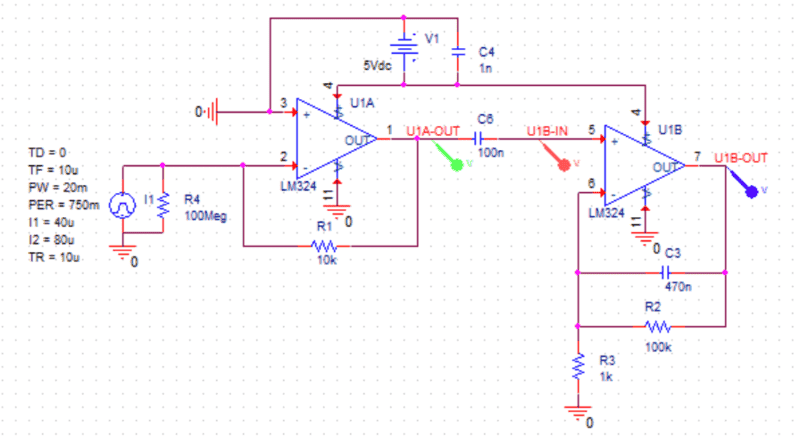

I am modelling a photodiode circuit which produces a small and periodic pulse with a small but potentially variable offset current. My circuit consists of a transimpedance amplifier to convert the small current into a voltage signal. The voltage signal is then filtered by a low pass filter. I wish to remove the small DC offset voltage but I cannot use a subtractor since the DC level may change.

My solution was to place a capacitor at the input of the low pass filter to remove the offset but allow any time-varying signals to be further filtered and amplified by the second stage.

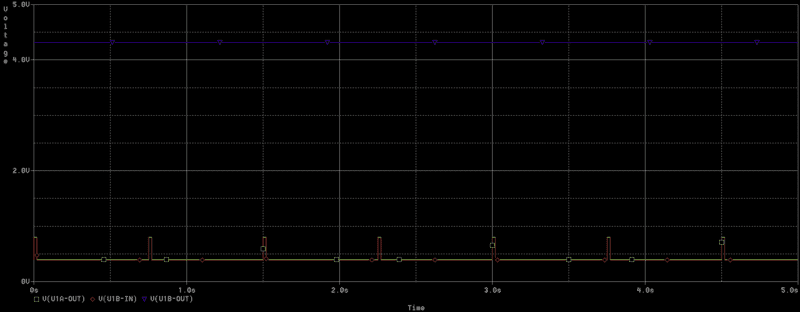

As you can see from my PSPICE simulation, the voltage after the capacitor is only slightly reduced and the DC level is not 0V. The output of my second stage has also satured for some reason.

Some help would be very appreciated!

My solution was to place a capacitor at the input of the low pass filter to remove the offset but allow any time-varying signals to be further filtered and amplified by the second stage.

As you can see from my PSPICE simulation, the voltage after the capacitor is only slightly reduced and the DC level is not 0V. The output of my second stage has also satured for some reason.

Some help would be very appreciated!