SUMMARY

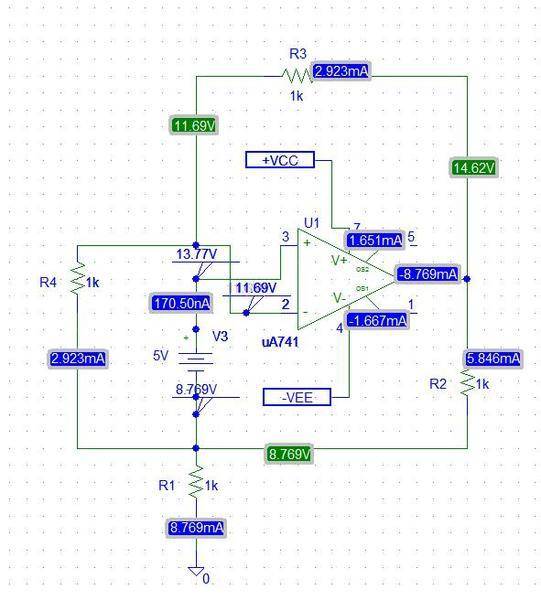

The discussion centers on unexpected voltage readings in a PSpice simulation involving an operational amplifier (op-amp) circuit using the uA741 model. The non-inverting terminal voltage is observed at 13.77V despite a 5V DC source being connected, due to the source being connected between an 8.769V point and the non-inverting input. The circuit's saturation is explained by the op-amp's gain of 200 V/mV, leading to discrepancies in expected voltages. To achieve ideal op-amp behavior in simulations, users are advised to select the "OPAMP" from the "ANALOG" library and adjust voltage limits accordingly.

PREREQUISITES

- Understanding of operational amplifier principles and configurations

- Familiarity with PSpice simulation software, specifically versions 9.1 and 9.2

- Knowledge of circuit analysis techniques, including nodal analysis

- Experience with the uA741 op-amp model and its characteristics

NEXT STEPS

- Learn how to configure ideal op-amps in PSpice simulations

- Research the characteristics and limitations of the uA741 op-amp model

- Explore advanced circuit analysis techniques to complement simulation results

- Investigate the impact of voltage supply limits on op-amp performance in simulations

USEFUL FOR

Electrical engineers, circuit designers, and students working with operational amplifiers and PSpice simulations who seek to understand voltage discrepancies in their circuit designs.