rugerts

- 153

- 11

- Homework Statement

- Find the branch currents.

- Relevant Equations

- KCL and Ohm's -> Node Voltage

Hello,

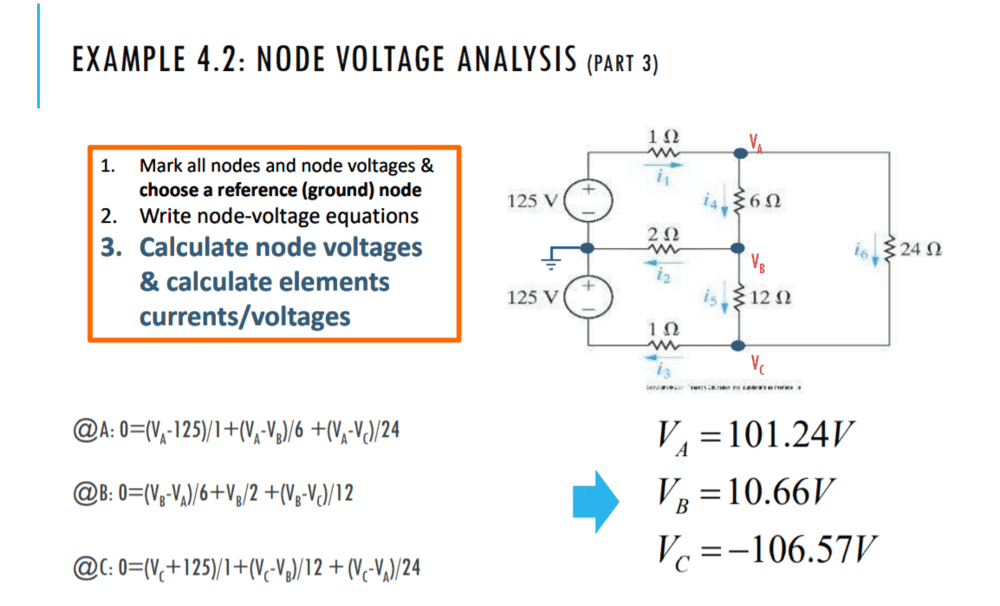

Here's the example I'm looking at now.

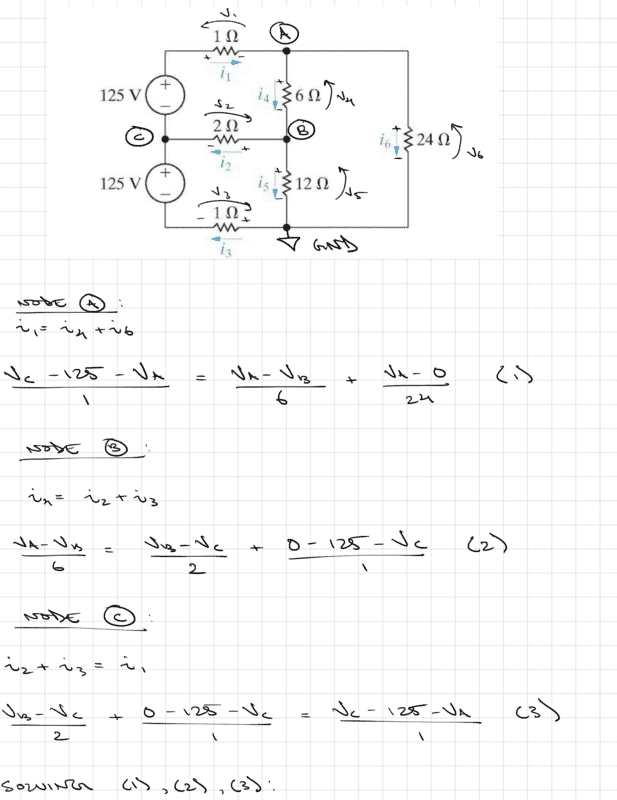

I am wondering if I swap ground and Node C... will this still be correct? I can see how it's more useful to have ground where it is above, but I'd still like to know if it would work for a swap of C and GND.

Here's my work trying this:

Does anyone see where I went wrong?

Here's the example I'm looking at now.

I am wondering if I swap ground and Node C... will this still be correct? I can see how it's more useful to have ground where it is above, but I'd still like to know if it would work for a swap of C and GND.

Here's my work trying this:

Does anyone see where I went wrong?