SUMMARY

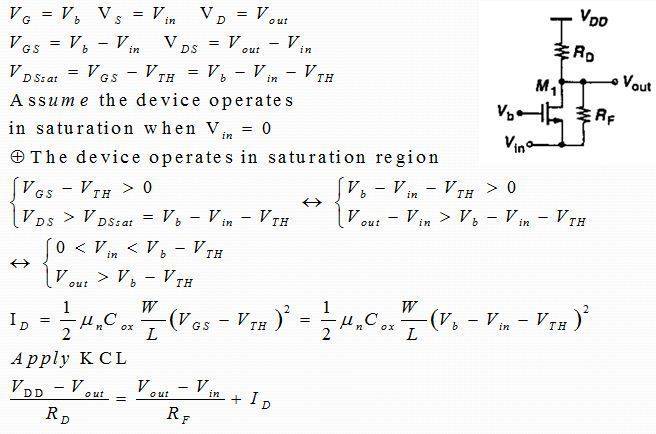

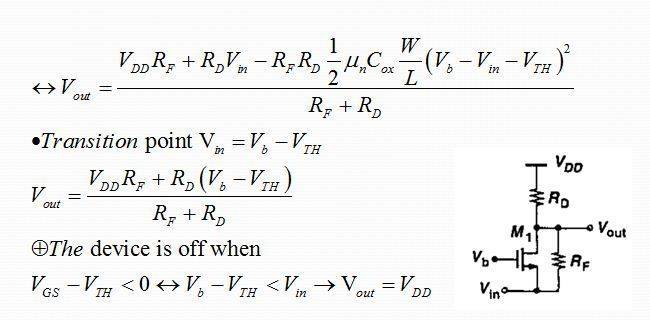

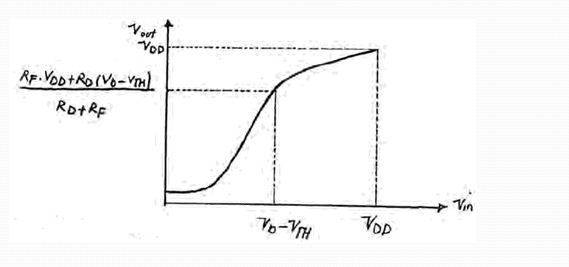

The discussion focuses on the common-gate configuration of MOS transistors, specifically analyzing the Vout versus Vin relationship as Vin varies from 0 to VDD. The circuit aims to enhance frequency response by mitigating the Miller effect through the inclusion of a small capacitance Cgd. Additionally, incorporating a feedback resistor Rf reduces the gain ∂Vout/∂Vin while providing some linearization, particularly in cutoff mode where ∂Vout/∂Vin equals R/Rf, with R being the parallel combination of Rd and Rf.

PREREQUISITES

- MOS transistor operation in triode and saturation modes

- Common-gate configuration principles

- Miller effect in electronic circuits

- Feedback resistor impact on gain and linearization

NEXT STEPS

- Study the effects of capacitance in MOS transistor configurations

- Learn about the Miller effect and its implications in circuit design

- Explore feedback mechanisms in amplifier circuits

- Investigate the mathematical modeling of MOS transistor gain

USEFUL FOR

Electrical engineers, circuit designers, and students studying analog electronics who are interested in MOS transistor configurations and their applications in improving frequency response.