NYAME EPHRAIM

- 10

- 1

< Mentor Note -- thread moved to HH from the technical forums, so no HH Template is shown >

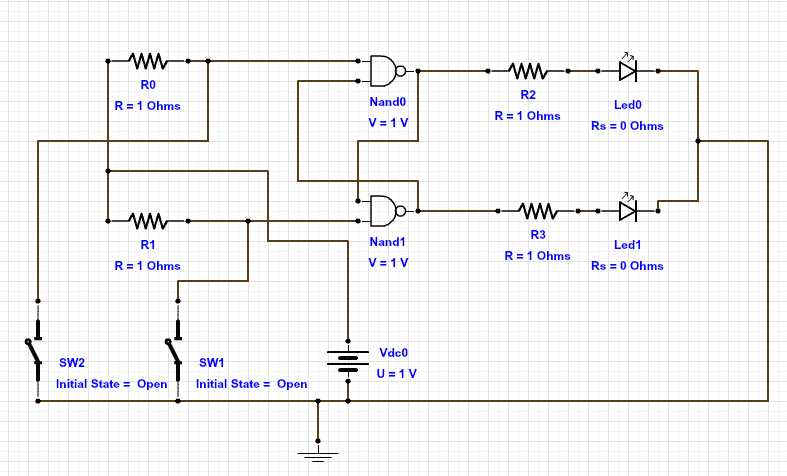

a) Using the Yenka (or similar) simulator, you are required to build an RS flip-flop using 2 NAND gates, switches, LEDs and 330Ω resistors. Test the circuit and prove its correct operation against the RS truth table, by print screening the 4 key modes and attaching a copy of your ‘RS flip-flop’ Yenka (or similar) file.

here is the diagram below i produced for the above task

a) Using the Yenka (or similar) simulator, you are required to build an RS flip-flop using 2 NAND gates, switches, LEDs and 330Ω resistors. Test the circuit and prove its correct operation against the RS truth table, by print screening the 4 key modes and attaching a copy of your ‘RS flip-flop’ Yenka (or similar) file.

here is the diagram below i produced for the above task

Attachments

Last edited by a moderator: