- #1

Mathhhew

- 20

- 1

- TL;DR Summary

- Two software give differents results with the same circuit

Hello!

I'm trying to model common mode current with LTSpice, but there is a problem with my simulation. Someone else tried on an other software and got the expected result, but I can't explain why. When going through the capacitor, square signals should become pulses, but that's not the case for me Here is the two screenshots:

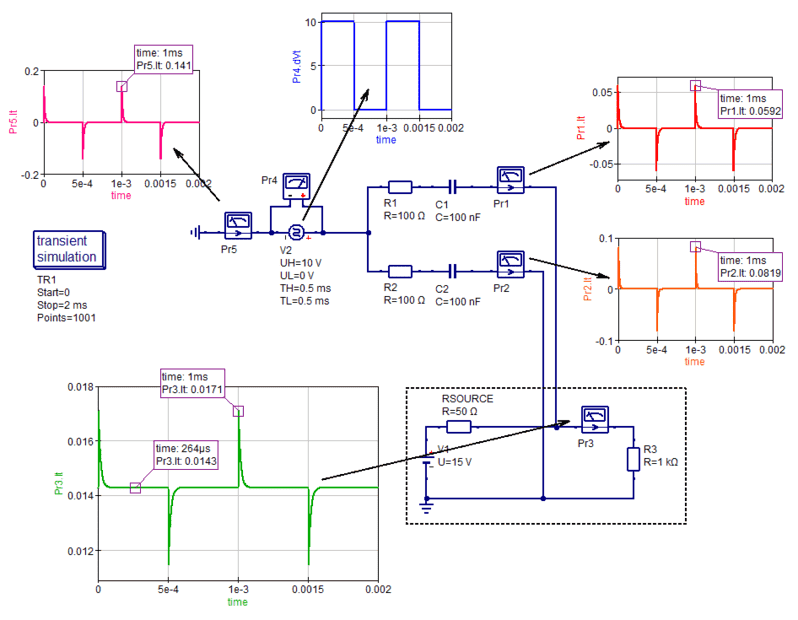

This is the one that shows the expected results

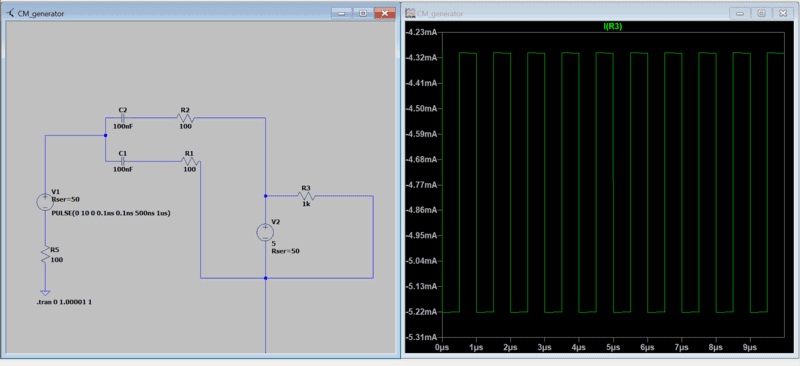

and mine

I'm trying to model common mode current with LTSpice, but there is a problem with my simulation. Someone else tried on an other software and got the expected result, but I can't explain why. When going through the capacitor, square signals should become pulses, but that's not the case for me Here is the two screenshots:

This is the one that shows the expected results

and mine