Discussion Overview

The discussion centers around the programming and application of AVX-512, particularly in the context of extracting column subtotals from a table of monthly expenses. Participants explore the implications of AMD's support for AVX-512 and its potential impact on software development and performance in consumer chips.

Discussion Character

- Technical explanation

- Debate/contested

- Exploratory

Main Points Raised

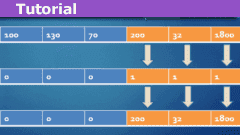

- One participant describes a program that calculates subtotals for various expense categories using AVX-512, emphasizing its efficiency in processing multiple values simultaneously.

- Another participant raises questions about the future popularity of AVX-512 now that AMD supports it, noting that its effectiveness is tied to the prevalence of CPUs that can utilize it.

- Concerns are expressed regarding Amdahl's Law and the competition from GPUs, which are already proficient at fused multiply-add operations.

- A participant reflects on their long-standing interest in SIMD operations and the historical context of AVX-512 support in Intel processors, suggesting that AMD's involvement may encourage broader software adoption.

- There is a critique of current parallelization approaches, arguing that many developers focus on CPU efficiency rather than leveraging the full capabilities of SIMD, which may hinder effective coding practices.

- Another participant notes that AMD's implementation of AVX-512 involves executing instructions through two sequential 256-bit operations, which may affect performance expectations.

Areas of Agreement / Disagreement

Participants express a range of views on the implications of AMD's support for AVX-512, with some optimistic about its potential for increased adoption, while others remain skeptical about its practical benefits and the challenges of parallelization. The discussion does not reach a consensus on these points.

Contextual Notes

Participants mention the complexity of AVX-512 instruction sets and the historical limitations of CPU support, which may influence software development decisions. There are also references to the challenges of optimizing code for parallel processing, indicating a need for further exploration of effective programming strategies.