nobrainer612

- 24

- 0

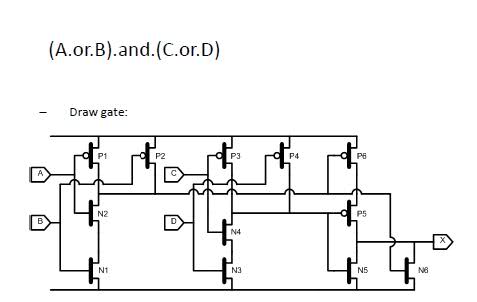

Hello. One of my friends told me that the logic function for (A.or.B).and.(C.or.D) is

From a book, I know the P1, P2 , N1, N2 form a NAND. The same for P3, P4, N3, N4.

And P5, P6, N5, N6 form a NOR.

My question is, is this circuit the same as (A.or.B).and.(C.or.D) ?

Thank you

From a book, I know the P1, P2 , N1, N2 form a NAND. The same for P3, P4, N3, N4.

And P5, P6, N5, N6 form a NOR.

My question is, is this circuit the same as (A.or.B).and.(C.or.D) ?

Thank you