SUMMARY

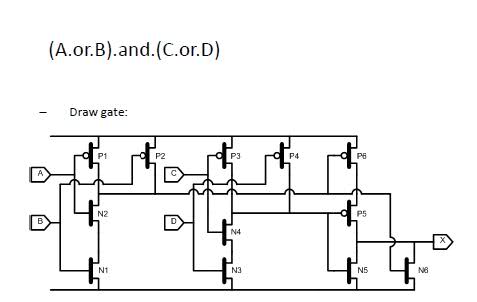

The discussion centers on the implementation of the logic function (A OR B) AND (C OR D) using CMOS gates. The circuit described utilizes NAND gates formed by P1, P2, N1, and N2, as well as NOR gates formed by P5, P6, N5, and N6. The output of the first stage is the NAND operation, followed by a NOR operation that combines the results, confirming that the circuit effectively represents the desired logic function. The final output is expressed as A.B.C.D, demonstrating the equivalence of the circuit to the original logic function.

PREREQUISITES

- Understanding of CMOS technology and gate configurations

- Familiarity with logic functions and Boolean algebra

- Knowledge of NAND and NOR gate operations

- Basic circuit design principles in digital electronics

NEXT STEPS

- Study CMOS gate design techniques for complex logic functions

- Learn about Boolean simplification methods to optimize logic circuits

- Explore the implementation of multi-stage logic circuits using NAND and NOR gates

- Investigate simulation tools for testing CMOS logic designs, such as LTspice or Multisim

USEFUL FOR

Electronics engineers, digital circuit designers, and students studying digital logic who are interested in implementing logic functions using CMOS technology.