Charismaztex

- 45

- 0

Hi,

I've read that some authors do not make the distinction that latches are level triggered (with clock of course) and flip-flops are edge-triggered and synchronized by the clock.

I am wondering, are there level-triggered flip-flops? My lecture notes says

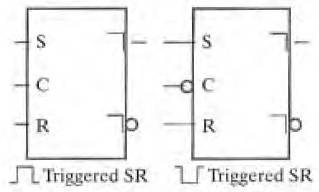

that this

is a level-triggered flip-flop as opposed to 2 rectangular blocks with dynamic-input indicators which would indicate edge triggering (what's the difference between this D master-slave flip-flop in the image and a, say, negative edge triggered D flip-flop as both changes occur at end of pulse?). Actually, are all D negative or positive edge triggered flip-flops master-slave flip-flops?

My understanding now is: (2 rectangular blocks as a whole) is an SR master-slave flip-flop and each rectangular block is a latch (which can be level triggered). Postponed output indicator indicates that output signal changes at end of, in case of SR master-slave flip-flop, edge of pulse (end of positive pulse for first block in image and end of negative pulse for second). Hence this implies that the master-slave flip-flop (if 2 rectangles or latches are considered as one flip-flop) or any flip-flop is edge triggered.

Is my understanding correct? I know the thinking is a little muddled so please help me clear it up and I think my lecture notes may be wrong. What's the verdict?

Thanks!

I've read that some authors do not make the distinction that latches are level triggered (with clock of course) and flip-flops are edge-triggered and synchronized by the clock.

I am wondering, are there level-triggered flip-flops? My lecture notes says

that this

is a level-triggered flip-flop as opposed to 2 rectangular blocks with dynamic-input indicators which would indicate edge triggering (what's the difference between this D master-slave flip-flop in the image and a, say, negative edge triggered D flip-flop as both changes occur at end of pulse?). Actually, are all D negative or positive edge triggered flip-flops master-slave flip-flops?

My understanding now is: (2 rectangular blocks as a whole) is an SR master-slave flip-flop and each rectangular block is a latch (which can be level triggered). Postponed output indicator indicates that output signal changes at end of, in case of SR master-slave flip-flop, edge of pulse (end of positive pulse for first block in image and end of negative pulse for second). Hence this implies that the master-slave flip-flop (if 2 rectangles or latches are considered as one flip-flop) or any flip-flop is edge triggered.

Is my understanding correct? I know the thinking is a little muddled so please help me clear it up and I think my lecture notes may be wrong. What's the verdict?

Thanks!