Discussion Overview

The discussion revolves around the layout of PMOS transistors, specifically focusing on the connection between the source and body of a PMOS device in a circuit design. Participants explore the implications of proper N-well connections and the layout strategies for optimizing performance and area in integrated circuit design.

Discussion Character

- Technical explanation

- Debate/contested

- Mathematical reasoning

Main Points Raised

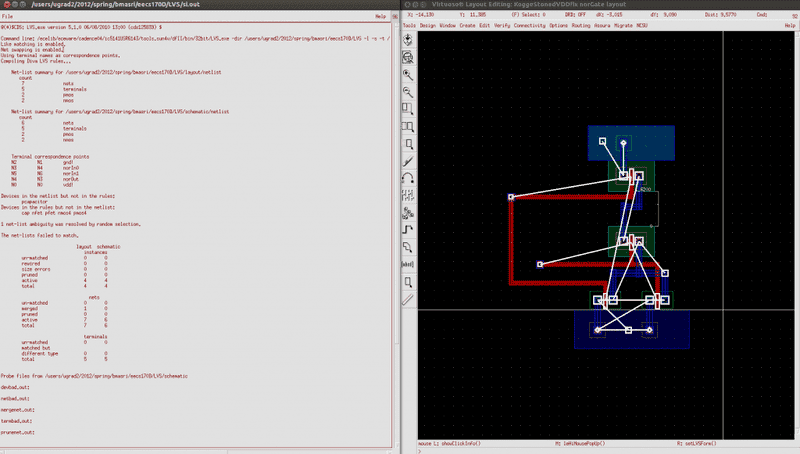

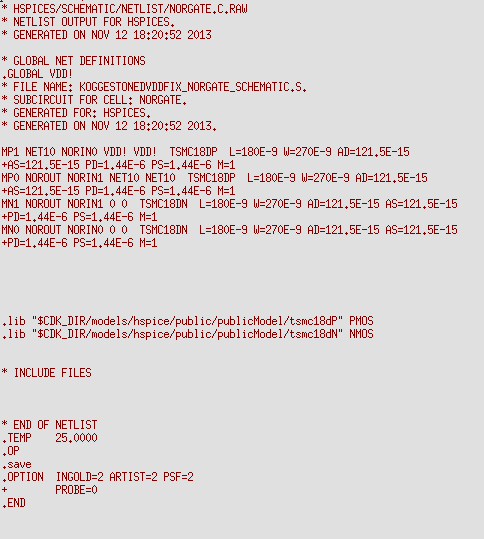

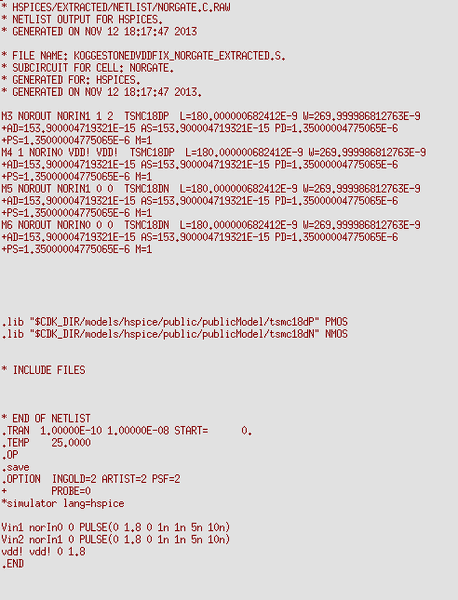

- One participant identifies a missing source-to-body connection in their PMOS layout and seeks guidance on how to establish this connection.

- Another participant suggests extending the N-well of the middle PMOS to connect with the upper PMOS's N-well to avoid floating wells, while also proposing an alternative of adding an N-well contact region.

- A participant expresses concern that extending the N-well may inadvertently connect the body of the middle PMOS to Vdd, questioning the relationship between the N-well and the PMOS body.

- Several participants emphasize that in logic circuits, PMOS bodies should be connected to Vdd to prevent forward biasing of source/drain junctions.

- There is a discussion about the efficiency of layouts, with one participant asking whether they need to construct transistors manually or if they can merge extracted transistors from a schematic.

- Another participant explains that aligning devices to share drains can minimize area and optimize performance, while also noting the importance of adhering to design rules regarding well spacing.

- One participant mentions the potential for using separate N-wells for specific design purposes, such as power management adjustments, despite the extra area required.

Areas of Agreement / Disagreement

Participants generally agree on the importance of connecting PMOS bodies to Vdd and the implications of N-well connections. However, there are differing views on the necessity and methods of constructing layouts, as well as the potential trade-offs involved in design choices.

Contextual Notes

Some participants express uncertainty about the implications of connecting N-wells and the specific design rules that apply, indicating that the discussion may depend on the context of the circuit's intended application and the design rules of the process technology used.

Who May Find This Useful

This discussion may be useful for circuit designers, students learning about PMOS layouts, and professionals involved in integrated circuit design who are interested in layout optimization and the implications of well connections.