SUMMARY

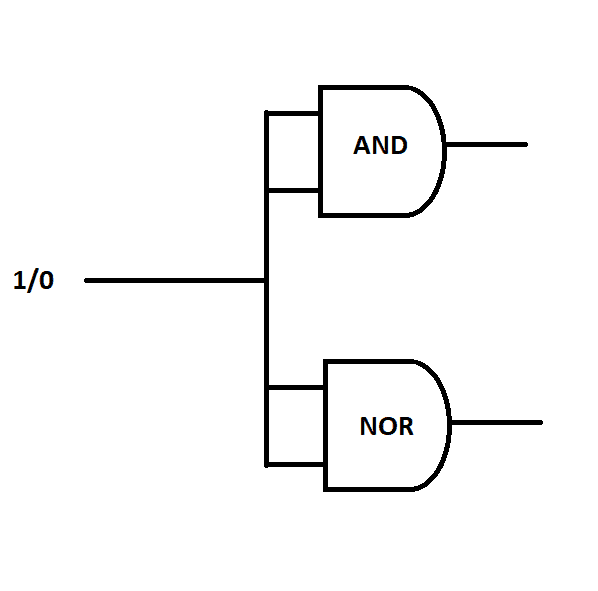

This discussion centers on the implications of tying both inputs of logic gates, specifically AND, OR, and NOR gates, together. It is established that this configuration can be used for signal conditioning and to introduce a 1-gate delay in the signal. The conversation also highlights potential issues with power consumption and signal integrity when connecting both inputs of a NAND gate, suggesting that connecting only one input may be more efficient in certain designs. The importance of considering circuit design and layout in relation to gate configurations is emphasized.

PREREQUISITES

- Understanding of basic logic gate functions (AND, OR, NOR, NAND)

- Familiarity with digital circuit design principles

- Knowledge of signal conditioning techniques

- Experience with PCB design and layout optimization

NEXT STEPS

- Research the impact of input loading on NAND gate performance

- Learn about signal integrity issues in digital circuits

- Explore techniques for optimizing PCB layouts for logic gates

- Investigate the use of simulation tools for digital circuit design

USEFUL FOR

Electronics engineers, digital circuit designers, and PCB designers looking to optimize logic gate configurations and improve circuit performance.