Michael Neo

- 49

- 3

- Homework Statement

- This question refers to the C68MX11 CPU, details of which accompany this assignment.

(Data sheet: http://www.moxsyn.com/data_sheets/C68MX11_cpu.pdf)

a) With reference to the block diagram of the CPU, what is the purpose of the program stack and the accumulators A, B and D?

b) Again with reference to the block diagram, outline how the processor would add two numbers held in ACC.A and ACC.B, the result being stored in memory.

Identify the addressing modes that would be employed in this addition.

c) Give the address range in hex that the PC could access.

- Relevant Equations

- None.

Part (a)

The Purpose of the Accumulators

The accumulator is a register for short-term, intermediate storage of arithmetic and logic data in a CPU.

(The term "accumulator" is rarely used in reference to contemporary CPUs, having been replaced around the turn of the millennium by the term "register". In a modern computers, any register can function as an accumulator. )

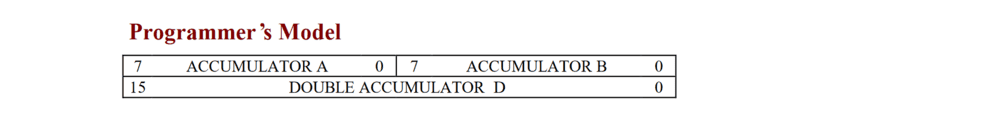

With reference to the block diagram of the CPU, although the data busses have a width of 8-bits most of the instructions have 16-bit equivalent instructions.

The C68MX11 offers multiply, add, subtract, compare, increment and decrement, load & store, and shift instructions of 16-bit operands.

The CPU consists of 8-bit accumulators used to hold operands and results of arithmetic calculations or data manipulations.

The accumulator A and B can be combined into a 16-bit double accumulator D that can store these 16-bit equivalent instructions.

From the data sheet:

The Purpose of the Program Stack

The Purpose of the Program Stack

From the data sheet: “The CPU automatically supports a program stack. This stack may be located anywhere in the 64 Kbyte address space through the stack pointer and may be any size up to the amount of memory available in the system.”

Definition

A stack is a data structure.

A stack is a linear data structure which follows a particular order in which the operations are performed.

A stack is an array of memory dedicated to temporary storage.

Structure

A stack is, typically, a LIFO data structure.

A stack stores data from the top down.

Function

A stack pointer is a register that stores, and is used to indicate, the address of the last item put onto the stack.

In this CPU, the stack is located anywhere in the 64 Kbyte address space via the stack pointer, and can be up to the amount of memory available in the system.

Part (b)

ACC.A and ACC.B are accumulators.

Accumulator A is the most significant octet while Accumulator B is the least significant octet.

The contents of these two 8-bit accumulators are fed into the ALU and then via the CCR are stored in Accumulator D.

Accumulators are used to store intermediate arithmetic and logic results and then fed to the next immediate level, i.e. the ALU.

OR

Add values stored in ACC.A and ACC.B and put the result in ACC.D, then run a separate cycle to store ACC.D in memory via the address bus and data port.

The binary operands are brought to the ALU via two inputs from ACC.A and ACC.B via the bus.

The addition takes place in the 16-bit ALU by adder circuits.

The 16 bit index registers IX and IY are used for indexed addressing modes.

The addressing modes that would be employed in this addition are:

1 KB = 1024 Bytes

64 KB = 65536 Bytes

So, address range = 0 to 65535

Convert decimal notation to hexadecimal,

0 = 0x0

65535 = 0xFFFF

Address range in hex,

0x0 to 0xFFFF

The Purpose of the Accumulators

The accumulator is a register for short-term, intermediate storage of arithmetic and logic data in a CPU.

(The term "accumulator" is rarely used in reference to contemporary CPUs, having been replaced around the turn of the millennium by the term "register". In a modern computers, any register can function as an accumulator. )

With reference to the block diagram of the CPU, although the data busses have a width of 8-bits most of the instructions have 16-bit equivalent instructions.

The C68MX11 offers multiply, add, subtract, compare, increment and decrement, load & store, and shift instructions of 16-bit operands.

The CPU consists of 8-bit accumulators used to hold operands and results of arithmetic calculations or data manipulations.

The accumulator A and B can be combined into a 16-bit double accumulator D that can store these 16-bit equivalent instructions.

From the data sheet:

From the data sheet: “The CPU automatically supports a program stack. This stack may be located anywhere in the 64 Kbyte address space through the stack pointer and may be any size up to the amount of memory available in the system.”

Definition

A stack is a data structure.

A stack is a linear data structure which follows a particular order in which the operations are performed.

A stack is an array of memory dedicated to temporary storage.

Structure

A stack is, typically, a LIFO data structure.

A stack stores data from the top down.

Function

A stack pointer is a register that stores, and is used to indicate, the address of the last item put onto the stack.

- When a new data item is entered or "pushed" onto the top of a stack, the stack pointer increments to the next physical memory address, and the new item is copied to that address.

- When a data item is "pulled" from the top of a stack, the item is copied from the address of the stack pointer, and the stack pointer decrements to the next available item at the top of the stack.

- Stack is a linear data structure.

- Typically, but not exclusively, LIFO.

- Stack Pointer is a register that indicates address of last item put on stack.

- Stack Pointer decreases when you put an item on the stack.

- Stack Pointer increases when you pull an item from the stack.

In this CPU, the stack is located anywhere in the 64 Kbyte address space via the stack pointer, and can be up to the amount of memory available in the system.

Part (b)

ACC.A and ACC.B are accumulators.

Accumulator A is the most significant octet while Accumulator B is the least significant octet.

The contents of these two 8-bit accumulators are fed into the ALU and then via the CCR are stored in Accumulator D.

Accumulators are used to store intermediate arithmetic and logic results and then fed to the next immediate level, i.e. the ALU.

OR

Add values stored in ACC.A and ACC.B and put the result in ACC.D, then run a separate cycle to store ACC.D in memory via the address bus and data port.

The binary operands are brought to the ALU via two inputs from ACC.A and ACC.B via the bus.

The addition takes place in the 16-bit ALU by adder circuits.

The 16 bit index registers IX and IY are used for indexed addressing modes.

The addressing modes that would be employed in this addition are:

- Direct

- Extended

- Indexed

1 KB = 1024 Bytes

64 KB = 65536 Bytes

So, address range = 0 to 65535

Convert decimal notation to hexadecimal,

0 = 0x0

65535 = 0xFFFF

Address range in hex,

0x0 to 0xFFFF

Last edited: