Discussion Overview

The discussion revolves around troubleshooting an analog delay line simulation in Multisim, focusing on the properties of transmission lines, including reflection and attenuation. Participants are examining the circuit design and simulation results, particularly in relation to low pass filters and their effectiveness in demonstrating the desired characteristics.

Discussion Character

- Technical explanation

- Debate/contested

- Experimental/applied

Main Points Raised

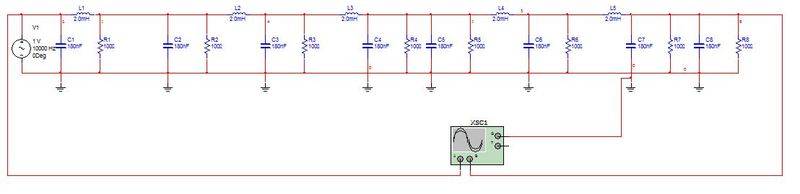

- One participant describes their attempt to construct an analog delay using low pass filters and reports not observing any reflections on the oscilloscope.

- Another participant requests waveform details and questions the utility of a capacitor in the circuit, as well as the output resistance of the voltage source.

- A participant shares their observed waveforms for sine and square pulse inputs, noting the presence of delay but absence of reflection effects.

- Questions are raised about the target characteristic impedance (Zo) of the transmission line, with one participant suggesting that the circuit appears lossy due to the resistor values used.

- Another participant emphasizes the importance of knowing the Zo to calculate expected reflections from mismatched terminations and critiques the high resistance values representing the dielectric conductance.

- A participant argues that the circuit as drawn may not function as a transmission line due to the configuration of the filter banks and suggests the need for inductance in the return path.

- This participant also notes that the time constant of each stage must be significantly greater than the signal's edge rate for the lumped model approximation to hold.

Areas of Agreement / Disagreement

Participants express differing views on the effectiveness of the current circuit design and the necessity of certain parameters, such as Zo. There is no consensus on the best approach to achieve the desired simulation outcomes, and multiple competing perspectives on circuit configuration and component values are present.

Contextual Notes

Participants highlight potential limitations in the circuit design, including assumptions about the reference potentials and the appropriateness of component values for achieving the desired transmission line behavior.