Discussion Overview

The discussion revolves around the behavior of a 555 timer circuit when the trigger switch is closed during a timing cycle. Participants explore the implications of this action on the circuit's operation, particularly focusing on waveform outputs and timing characteristics. The context includes simulation results and theoretical considerations regarding the 555 timer's functionality.

Discussion Character

- Exploratory

- Technical explanation

- Debate/contested

- Experimental/applied

Main Points Raised

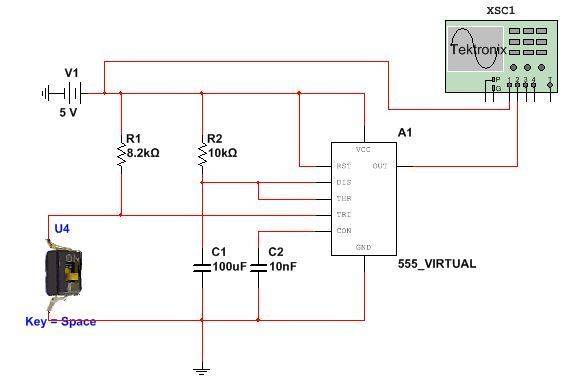

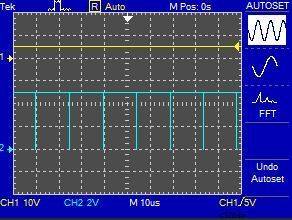

- One participant presents a circuit and waveform from a simulation, seeking clarification on the observed behavior when the trigger switch is closed during the timing cycle.

- Another participant suggests that the capacitor may not have enough time to charge, which could affect the timing cycle when the trigger is activated again.

- A participant calculates a time constant based on resistor and capacitor values, questioning the actual capacitance used in the simulation and suggesting a bypass capacitor for stability during switching.

- One participant references a datasheet, explaining the trigger requirements for the 555 timer and how holding the trigger low for too long can affect the output state, indicating that the output will follow the trigger signal in such cases.

- A later reply expresses skepticism about the simulation results, emphasizing that different manufacturers' 555 timers may behave differently under non-standard configurations.

Areas of Agreement / Disagreement

Participants express differing views on the behavior of the 555 timer in this scenario, with no consensus reached on the implications of closing the switch during the timing cycle. Some participants provide theoretical insights while others question the reliability of the simulation results.

Contextual Notes

Limitations include potential discrepancies in component values, the nature of the simulation versus real-world behavior, and variations in 555 timer models from different manufacturers that may affect performance.