- #1

akaliuseheal

- 53

- 8

Hello,

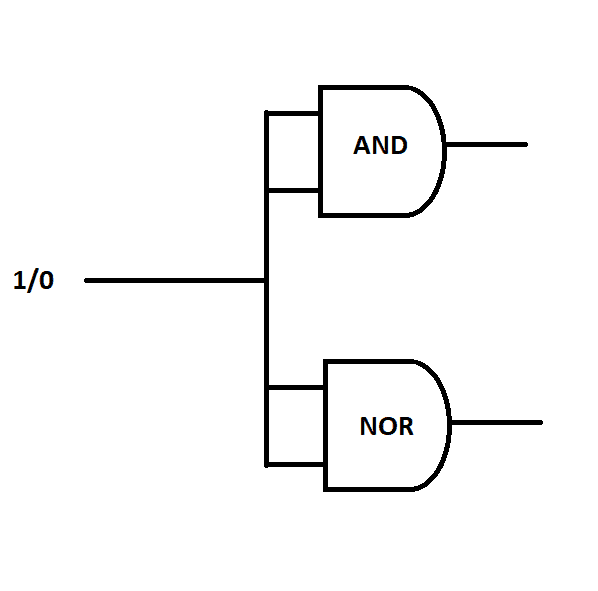

I don't know much about logic gates and how they work.

I was wondering if this (Image) can work. (Is something like this possible?)

The idea is that if we have logic 1, AND gate gives 1 while NOR gives 0. And vice versa.

I don't know much about logic gates and how they work.

I was wondering if this (Image) can work. (Is something like this possible?)

The idea is that if we have logic 1, AND gate gives 1 while NOR gives 0. And vice versa.

Attachments

Last edited by a moderator: