Discussion Overview

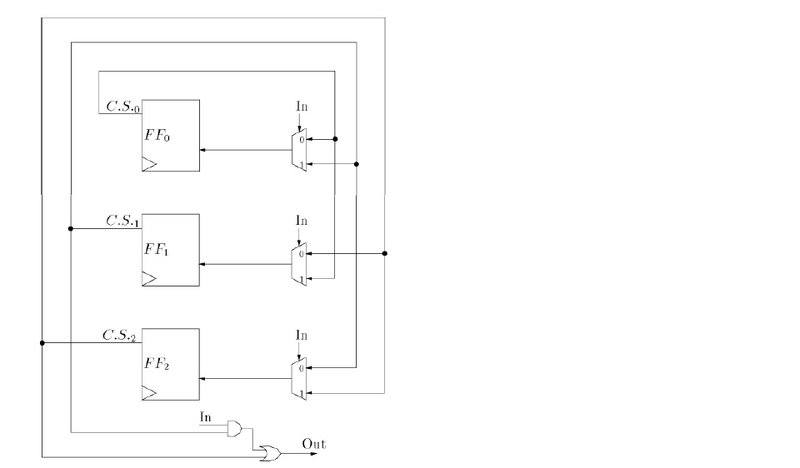

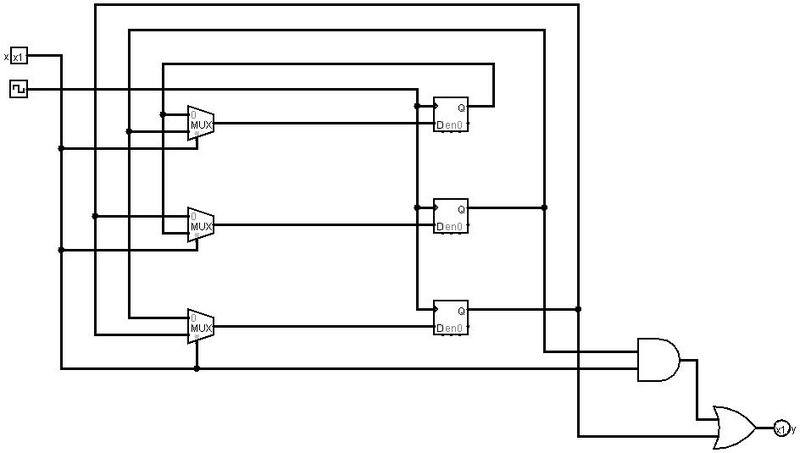

The discussion revolves around troubleshooting a logic circuit implemented in Logisim, specifically focusing on the initialization of D flip-flops (DFFs) and the expected behavior of a finite state machine (FSM) designed to compute the quotient of x/3. Participants are exploring the configuration and connections necessary to achieve the desired output.

Discussion Character

- Technical explanation

- Debate/contested

- Homework-related

- Mathematical reasoning

Main Points Raised

- One participant reports that their circuit consistently outputs y=0 and seeks feedback on potential issues.

- Another participant suggests that if the D-flops start in state Q=0, then y=0 is the expected output regardless of the input X.

- Concerns are raised about the DFF inputs being driven by outputs of other DFFs, questioning how a 1 can be generated if all start at zero.

- Participants discuss the need to set the initial state of the DFFs and how to connect a reset button to initialize them properly.

- Some participants provide insights into the behavior of the FSM, explaining how the state transitions occur based on the input and the current state.

- There is a discussion about the number of DFFs required for the implementation, with some arguing that only two are necessary to represent the states of the FSM.

- One participant expresses confusion about the initialization process in Logisim and requests clarification on how to set the initial state to 001.

- Another participant explains how to use the Set, Enable, and Clear terminals of the DFFs to establish the initial state and suggests creating a reset pulse.

- Participants engage in clarifying the connections needed for the reset and input signals, with some expressing uncertainty about the correct configuration.

Areas of Agreement / Disagreement

There is no clear consensus on the correct initialization method for the DFFs or the necessary connections for the reset functionality. Multiple competing views on the implementation details and the number of DFFs required persist throughout the discussion.

Contextual Notes

Participants reference specific states and transitions of the FSM without fully resolving the implications of their configurations. There are also mentions of various interpretations of the connections needed for the DFFs, indicating potential misunderstandings or ambiguities in the setup.

Who May Find This Useful

This discussion may be useful for individuals working on digital logic design, particularly those using Logisim for implementing finite state machines and troubleshooting related issues.