Master1022

- 590

- 116

- Homework Statement

- 1) What is the point of having another (low-pass) filter ## G_f (s) ## for ## V_o ## after already passing the voltage through a low pass filter?

2) Is there any particular relationship between the bandwidth of the low pass filter and the locking range of the PLL?

- Relevant Equations

- LPF

Hi,

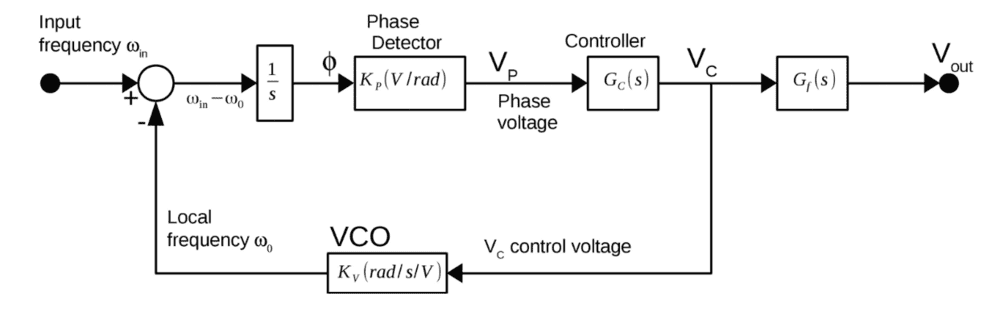

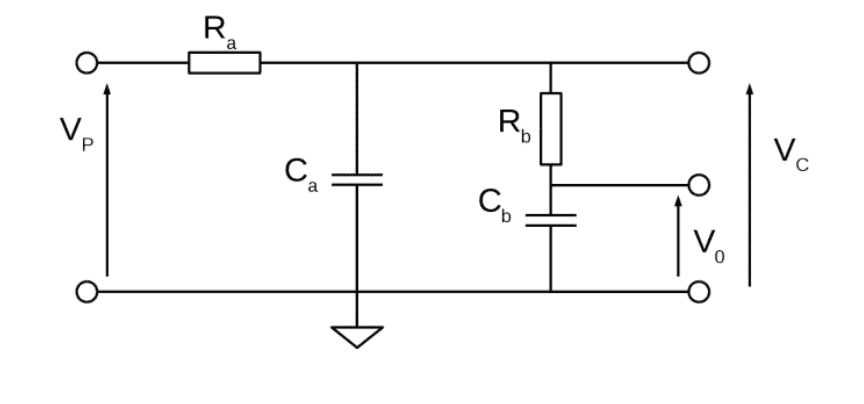

I had one or two questions about the operation of a PLL, which refer to the diagrams below - a control representation of the system and a diagram of the low pass filter circuit.

Questions:

1) What is the point of having another (low-pass) filter ## G_f (s) ## for ## V_o ## after already passing the voltage through a low pass filter?

I know that we want to filter the pulses output from the phase detector to form a voltage to input into the VCO. However, why is there another filter ## G_f (s) ## that acts before the output ## V_o##?

2) Is there any particular relationship between the bandwidth of the low pass filter and the locking range of the PLL?

I think I am slightly confused as to what these terms mean. Is the locking range the frequency range over which the PLL works (i.e. can detect signal frequencies between ## x ## and ## y ##)? The bandwidth of the low pass filter determines the speed of response of the PLL?

Any help is greatly appreciated.

I had one or two questions about the operation of a PLL, which refer to the diagrams below - a control representation of the system and a diagram of the low pass filter circuit.

Questions:

1) What is the point of having another (low-pass) filter ## G_f (s) ## for ## V_o ## after already passing the voltage through a low pass filter?

I know that we want to filter the pulses output from the phase detector to form a voltage to input into the VCO. However, why is there another filter ## G_f (s) ## that acts before the output ## V_o##?

2) Is there any particular relationship between the bandwidth of the low pass filter and the locking range of the PLL?

I think I am slightly confused as to what these terms mean. Is the locking range the frequency range over which the PLL works (i.e. can detect signal frequencies between ## x ## and ## y ##)? The bandwidth of the low pass filter determines the speed of response of the PLL?

Any help is greatly appreciated.