Frank-95

- 51

- 1

Hi all!

I am trying to simulate a differential amplifier in LTSpice but I'm having some troubles.

First, I would like to know if you could suggest me some "basic", scholastic, MOSFET and BJT model, like the 1N4148 for diodes.

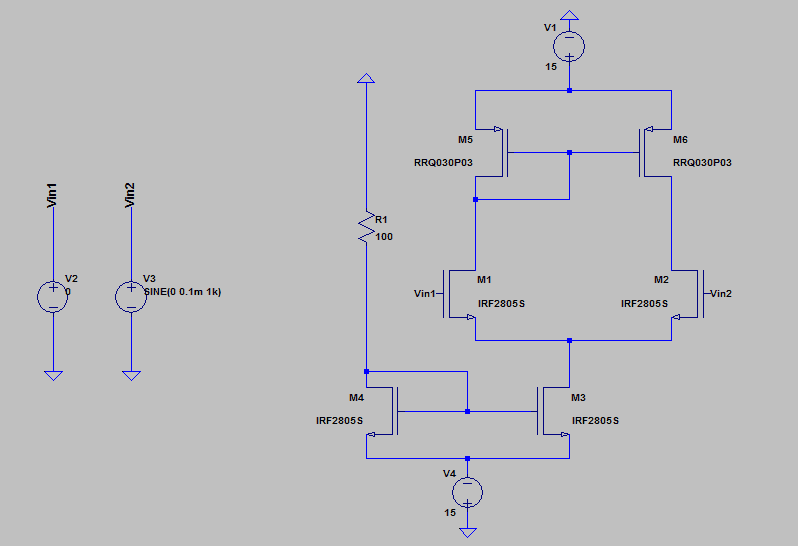

Secondly I designed this:

Practically when I get the drain output I have a big amplification but with a HUGE DC offset: 12 volts about!

Do you know why?Did I mistaken somehitng?

Moreover I don't remember a thing from my electronics studies: should R1 be linked to ground or to V1?

Thank you very much

I am trying to simulate a differential amplifier in LTSpice but I'm having some troubles.

First, I would like to know if you could suggest me some "basic", scholastic, MOSFET and BJT model, like the 1N4148 for diodes.

Secondly I designed this:

Practically when I get the drain output I have a big amplification but with a HUGE DC offset: 12 volts about!

Do you know why?Did I mistaken somehitng?

Moreover I don't remember a thing from my electronics studies: should R1 be linked to ground or to V1?

Thank you very much