- #1

Femme_physics

Gold Member

- 2,550

- 1

Last edited by a moderator:

I like Serena said:No exaggeration.

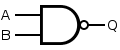

But shouldn't each NAND gate have exactly 2 inputs?

Like this:

And you appear to have drawn a thin rectangle before each NAND gate.

What does that represent?

I intended to try and get the answer for the question but if there's a + C then I made a mistake it appears. What I really wanted is what you wrote at the end of that post. Is it all about just trying to build it via experience or is it about building a truth table and doing it methodically and schematically in a straightforward fashion?Is that what you intended?

Femme_physics said:I intended to try and get the answer for the question but if there's a + C then I made a mistake it appears. What I really wanted is what you wrote at the end of that post. Is it all about just trying to build it via experience or is it about building a truth table and doing it methodically and schematically in a straightforward fashion?

Whatever works for you.

Systematic and methodical is good. :)

On the wiki page for NAND logic, they give a couple of building blocks to create the various logic operations:

http://en.wikipedia.org/wiki/NAND_logic

With it you can build up your schematic.

Femme_physics said:I understand what you mean-- and I think I got it

A logical gate function is a basic building block of digital circuits that performs a specific logical operation on one or more binary inputs and produces a single binary output.

A NAND gate is a type of logical gate that produces an output of 0 only when all of its inputs are 1. It is a combination of an AND gate and a NOT gate.

NAND gates are considered universal gates, which means that all other logical gate functions can be built using only NAND gates. This simplifies the design process and reduces the number of components needed.

To build a logical gate function using only NAND gates, the inputs can be connected to the inputs of multiple NAND gates, and the outputs of those NAND gates can be connected to the inputs of a final NAND gate. The output of this final NAND gate will be the desired output of the logical gate function.

Using only NAND gates in logical gate functions can reduce the number of components needed, simplify the design process, and allow for easier troubleshooting and maintenance of the circuit.