tim9000

- 866

- 17

Hi,

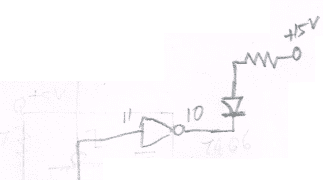

Can current flow both ways through a NOT gate, or is the diagram I saw, much like the picture I drew here, just drawn the wrong way around?

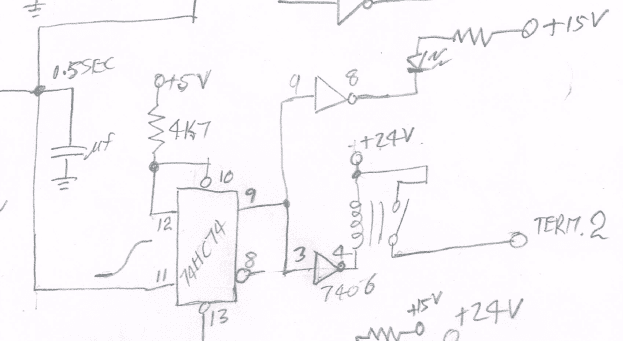

Anyway, say it was correct, so what does this mean? Because the chip itself (the not gate chip Vcc = 5V and Gnd) takes 5V between it and the chip ground. So when the 15V is active, pin 11 gets inverted to 0V? and When 15V is not active, what is pin 11? Is it then 5V? (So it is never 15V?)

For a larger context on what I'm trying to figure out:

It seems like the not gates and the LED and relay coil, are flowing backwards? Because Pin 9 of the flip flop is Q.

How does the current flow to or from pin 9? If pin 9 is high because it was pulsed with data on the clock then presumably pin 9 is 5V? (from Pin 12 and pin 10)? But 5V with reference to what ground?

Where the chip is:

Thanks!

(I can provide more info on the diagram if needed)

Can current flow both ways through a NOT gate, or is the diagram I saw, much like the picture I drew here, just drawn the wrong way around?

Anyway, say it was correct, so what does this mean? Because the chip itself (the not gate chip Vcc = 5V and Gnd) takes 5V between it and the chip ground. So when the 15V is active, pin 11 gets inverted to 0V? and When 15V is not active, what is pin 11? Is it then 5V? (So it is never 15V?)

For a larger context on what I'm trying to figure out:

It seems like the not gates and the LED and relay coil, are flowing backwards? Because Pin 9 of the flip flop is Q.

How does the current flow to or from pin 9? If pin 9 is high because it was pulsed with data on the clock then presumably pin 9 is 5V? (from Pin 12 and pin 10)? But 5V with reference to what ground?

Where the chip is:

Thanks!

(I can provide more info on the diagram if needed)