PainterGuy

- 938

- 73

Hi,

I'm trying to learn Verilog and was exploring different ways to write a simple Verilog code for Arithmetic Logic Unit, ALU. I was going through this webpage: https://esrd2014.blogspot.com/p/8-bit-arithmetic-and-logic-unit.html

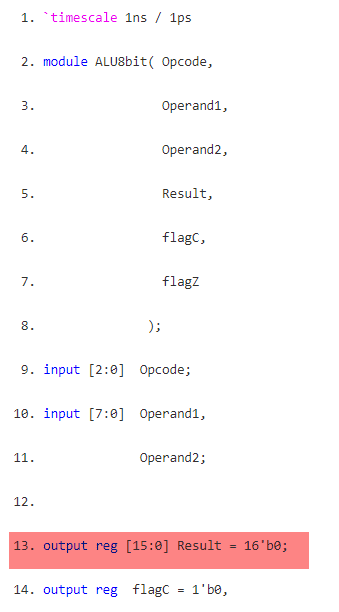

I'm just curious to know that why they are using 16 bit output register' please see the capture below taken from the mentioned webpage. They could have simply used 9 bit register instead. Is the reason being that the registers come in standard sizes such 8-bit, 16-bit, 32-bit, etc.?

Actually, I'm planning to modify the given code to come up with a simple ALU code but I thought to confirm about the 16-bit output register first. Thanks for the help, in advance!

I'm trying to learn Verilog and was exploring different ways to write a simple Verilog code for Arithmetic Logic Unit, ALU. I was going through this webpage: https://esrd2014.blogspot.com/p/8-bit-arithmetic-and-logic-unit.html

I'm just curious to know that why they are using 16 bit output register' please see the capture below taken from the mentioned webpage. They could have simply used 9 bit register instead. Is the reason being that the registers come in standard sizes such 8-bit, 16-bit, 32-bit, etc.?

Actually, I'm planning to modify the given code to come up with a simple ALU code but I thought to confirm about the 16-bit output register first. Thanks for the help, in advance!