PhysicsTruth

- 117

- 18

Thread moved from the technical forums to the schoolwork forums

Summary:: Using a common emitter amplifier to pump up the input voltage, and studying the effects henceforth.

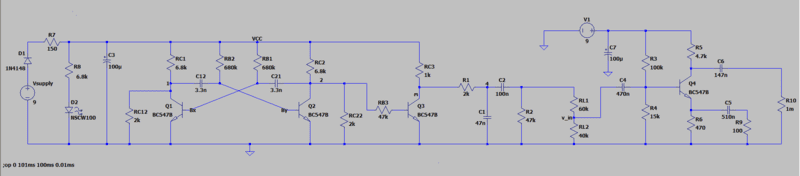

Here is a circuit with 0.6V pk-pk input voltage (v_in) for the CE amplifier, 1.17 kHz frequency-

For this, without C5 and R9, the AC and DC gain was -10. I was supposed to increase the AC gain to -50 while keeping DC gain intact, so I added C5 and R9 in order to get that. I was supposed to play around with only the emitter leg. It would be nice if someone would confirm if I did it correctly, keeping in mind that frequency for the high pass filter at 3dB is 100 Hz. Also, a lot of non-linearity is observed in the AC gain, which I don' t seem to understand.

The main thing is that, I'm supposed to study the effect of connecting a load impedance from C6 to ground and measuring the output voltage there. Without R10, ##V_{E}## had a peak of 8.8V approx, which is justified by the quiescent collector current, but why did the voltage after C6 drop to around 4.9V? I can't seem to find out. Also, according to me, R10 creates a voltage divider bias, thus ##V_{E}## should be thus 8.8 * 4.7/9.4, which is roughly 4.4 V. Surprisingly, the simulation gives me a peak of about 6.5V for ##V_{E}##, and the voltage measured between C6 and R10 gives me around 2.4 V. This is supposed to be a voltage divider, since I observed that when R10 is very high, normalcy is retained. But, how to calculate these voltages using appropriate equations, as my calculations don't comply with the simulation's?

Here is a circuit with 0.6V pk-pk input voltage (v_in) for the CE amplifier, 1.17 kHz frequency-

For this, without C5 and R9, the AC and DC gain was -10. I was supposed to increase the AC gain to -50 while keeping DC gain intact, so I added C5 and R9 in order to get that. I was supposed to play around with only the emitter leg. It would be nice if someone would confirm if I did it correctly, keeping in mind that frequency for the high pass filter at 3dB is 100 Hz. Also, a lot of non-linearity is observed in the AC gain, which I don' t seem to understand.

The main thing is that, I'm supposed to study the effect of connecting a load impedance from C6 to ground and measuring the output voltage there. Without R10, ##V_{E}## had a peak of 8.8V approx, which is justified by the quiescent collector current, but why did the voltage after C6 drop to around 4.9V? I can't seem to find out. Also, according to me, R10 creates a voltage divider bias, thus ##V_{E}## should be thus 8.8 * 4.7/9.4, which is roughly 4.4 V. Surprisingly, the simulation gives me a peak of about 6.5V for ##V_{E}##, and the voltage measured between C6 and R10 gives me around 2.4 V. This is supposed to be a voltage divider, since I observed that when R10 is very high, normalcy is retained. But, how to calculate these voltages using appropriate equations, as my calculations don't comply with the simulation's?