Discussion Overview

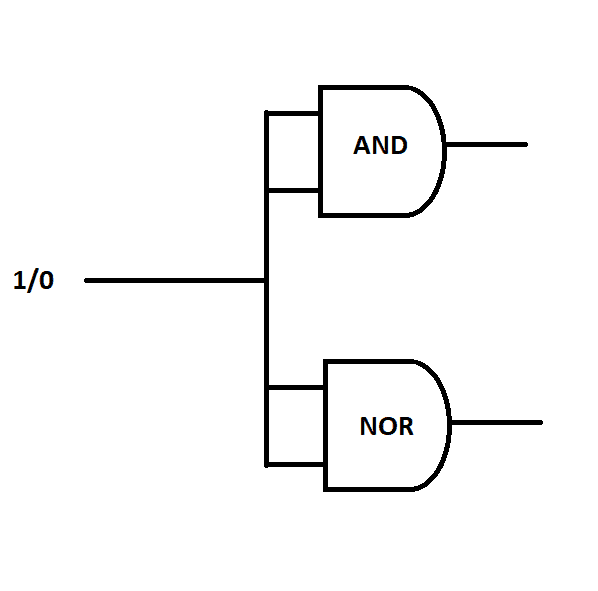

The discussion revolves around the configuration of logic gates, specifically the implications of tying both inputs of gates together. Participants explore the functionality of AND, NOR, and NAND gates in this context, considering both theoretical and practical aspects of digital logic design.

Discussion Character

- Exploratory

- Technical explanation

- Debate/contested

- Mathematical reasoning

Main Points Raised

- Some participants suggest that tying both inputs of an AND or NOR gate can work for signal conditioning or to introduce a delay.

- Others pose quiz questions regarding the outputs of gates when given specific input sequences, indicating a focus on understanding gate behavior.

- Concerns are raised about potential issues when using a NAND gate as an inverter, with some participants questioning the rationale behind tying inputs together versus connecting only one input.

- Participants discuss the implications of increased power requirements and loading effects when connecting multiple inputs to a gate.

- Some argue that tying inputs together can simplify circuit design and save space on a PCB, while others caution against potential timing inconsistencies and signal integrity issues.

Areas of Agreement / Disagreement

There is no consensus on the best approach to configuring gate inputs, with multiple competing views and concerns raised about the implications of different configurations.

Contextual Notes

Participants mention various considerations such as power consumption, signal timing, and PCB design, but do not resolve the complexities involved in these design choices.

Who May Find This Useful

This discussion may be of interest to electronics engineers, students studying digital logic design, and hobbyists working on circuit design projects.