Discussion Overview

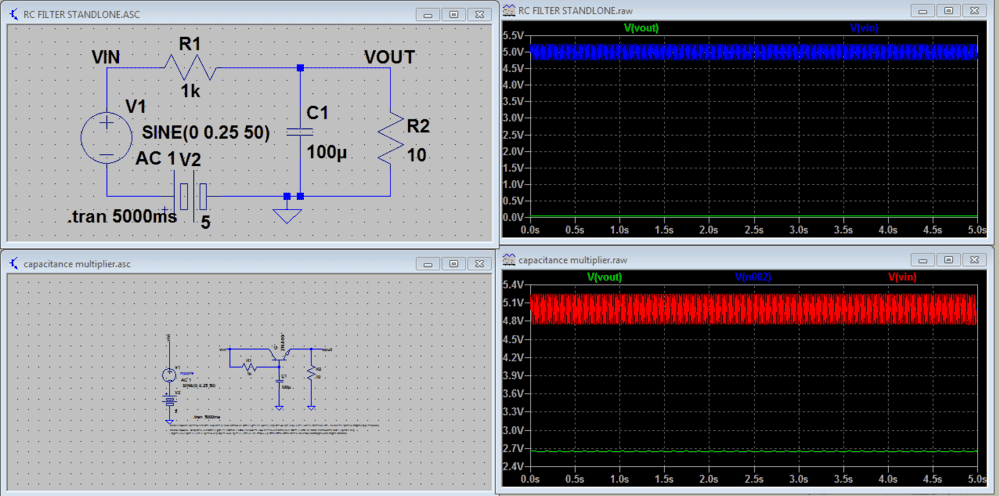

The discussion revolves around measuring ripple reduction in capacitance multiplier circuits compared to RC filter circuits using LTSpice simulations. Participants are exploring how to accurately measure and interpret ripple voltages in their simulations, as well as the operational characteristics of capacitance multipliers.

Discussion Character

- Exploratory

- Technical explanation

- Debate/contested

- Mathematical reasoning

Main Points Raised

- One participant seeks guidance on measuring ripple reduction in LTSpice simulations, specifically comparing a capacitance multiplier circuit to an RC filter.

- Another participant suggests using the .MEASure command in LTSpice to measure ripple voltage and emphasizes the importance of retaining the log file for results.

- A participant reports unexpected results, indicating that the ripple voltage of the capacitance multiplier is higher than that of the RC filter, questioning the effectiveness of the circuit.

- Some participants express uncertainty about the circuit design, suggesting potential missing components, such as a resistor for biasing the transistor.

- There is discussion about the operational modes of the transistor in the capacitance multiplier, with some participants debating whether saturation is beneficial or detrimental for ripple suppression.

- One participant provides external resources for further understanding of capacitance multipliers and their design considerations.

- Another participant clarifies the conditions for transistor saturation and its implications for circuit performance.

- Some participants express confusion regarding the role of saturation in the context of ripple suppression and the relationship between transistor gain and capacitance.

- A participant acknowledges a mistake in terminology regarding saturation, indicating a mix-up with MOSFET amplifiers.

Areas of Agreement / Disagreement

Participants express differing views on the effectiveness of capacitance multipliers in reducing ripple, with some questioning the circuit design and others debating the implications of transistor saturation. The discussion remains unresolved regarding the optimal design and measurement techniques.

Contextual Notes

Participants mention potential limitations in their circuit designs and measurements, including the need for specific component values and configurations to achieve desired performance. There is also uncertainty regarding the operational characteristics of the circuits being discussed.