- 29,204

- 4,627

(in a way this is a continuation of the previous thread on the solution choosing strategy)

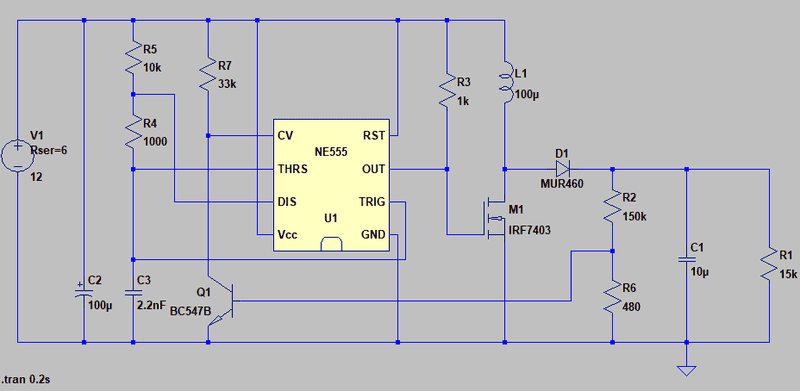

So, I needed DC-DC switcher, capable of delivering up to 200 V and 10 mA. Idea is simple - coil, interrupting the current, "collecting" the voltage. Easy to implement with 555, but difficult to control the output voltage with just frequency and duty cycle of oscillations. Some googling (this is switcher for a Niхie clock and I am not a first one to build it) yields this solution (element values can be different and actually R6 is a potentiometer allowing to control the voltage on the load R1):

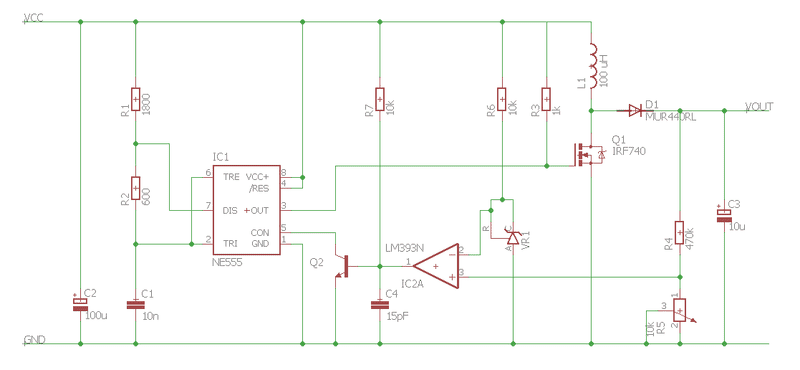

What I don't like about it is that the output voltage depends on both the V1 voltage and R1 resistance. But I liked the idea of using CV (AKA CON) to change the duty cycle, so I decided to try a bit different approach, with a voltage reference and comparator:

In theory VOUT should not depend on the load nor VCC. I tested a very similar circuit in the LTSpice:

(it is not identical to the one I build as I couldn't find LTSpice models for LM393N comparator nor KA431LZ voltage reference, so I used a functionally equivalent chip from the program library). Green - voltage on the load (VOUT), red - current drawn from V1, blue - current through L1.

Long story short - it works not only in the simulation, but also on a breadboard. I have built a prototype and it powers my clock right now. No elements get hot, voltage looks stable (it is at 162 V now, and floats by about ±0.2), it does change a bit with load and VCC, but I have not yet tested it too heavily to see by how much.

Comments welcome.

(sorry, looks like PF resized pictures, I hope they will be readable)

So, I needed DC-DC switcher, capable of delivering up to 200 V and 10 mA. Idea is simple - coil, interrupting the current, "collecting" the voltage. Easy to implement with 555, but difficult to control the output voltage with just frequency and duty cycle of oscillations. Some googling (this is switcher for a Niхie clock and I am not a first one to build it) yields this solution (element values can be different and actually R6 is a potentiometer allowing to control the voltage on the load R1):

What I don't like about it is that the output voltage depends on both the V1 voltage and R1 resistance. But I liked the idea of using CV (AKA CON) to change the duty cycle, so I decided to try a bit different approach, with a voltage reference and comparator:

In theory VOUT should not depend on the load nor VCC. I tested a very similar circuit in the LTSpice:

(it is not identical to the one I build as I couldn't find LTSpice models for LM393N comparator nor KA431LZ voltage reference, so I used a functionally equivalent chip from the program library). Green - voltage on the load (VOUT), red - current drawn from V1, blue - current through L1.

Long story short - it works not only in the simulation, but also on a breadboard. I have built a prototype and it powers my clock right now. No elements get hot, voltage looks stable (it is at 162 V now, and floats by about ±0.2), it does change a bit with load and VCC, but I have not yet tested it too heavily to see by how much.

Comments welcome.

(sorry, looks like PF resized pictures, I hope they will be readable)