Discussion Overview

The discussion revolves around the simulation of a differential amplifier using LTSpice, focusing on issues related to voltage offset, component models, and circuit design choices. Participants explore both MOSFET and BJT configurations, as well as the implications of various design decisions on the amplifier's performance.

Discussion Character

- Exploratory

- Technical explanation

- Debate/contested

- Mathematical reasoning

Main Points Raised

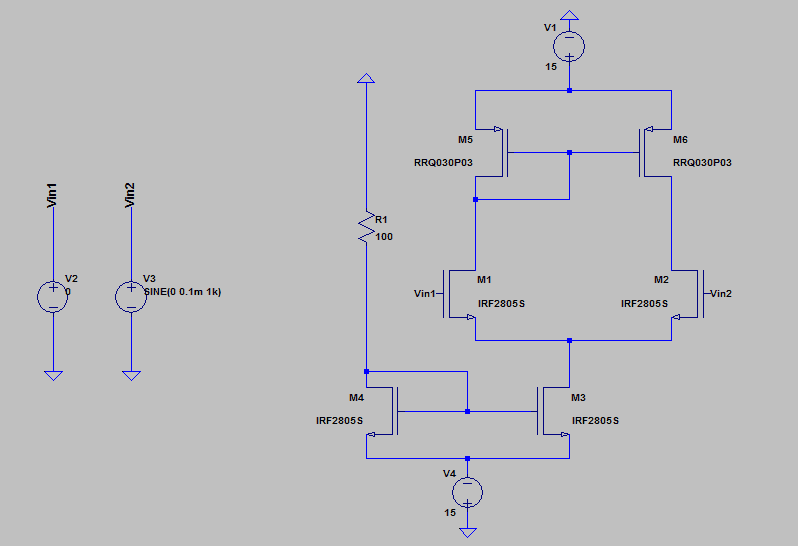

- One participant seeks basic MOSFET and BJT models for simulation, similar to the 1N4148 diode.

- Another suggests that the drain of M1 should match the voltage of M2 and recommends using a dual matched pair of MOSFETs.

- A participant expresses a desire to minimize the number of resistors in the design, questioning the source of the significant voltage offset in their circuit.

- Concerns are raised about the accuracy of the LTSpice simulation results compared to textbook values, with a specific model for NMOS transistors provided.

- One participant attributes the DC offset to channel length modulation effects, suggesting adjustments to the positive supply voltage to equalize drain potentials.

- Another participant notes that the amplifier is operating in open loop and questions the reference point for measuring the DC offset.

- Discussion includes the role of bypass capacitors in multistage op-amps and whether DC components are maintained across stages.

- Clarification is provided that negative feedback is typically used to set DC conditions in such circuits.

- Participants discuss the adequacy of the NMOS model used in simulations, with one confirming that it produces expected results under certain conditions.

- One participant encounters unexpected current values in their circuit and receives advice on correcting transistor designations in the simulation.

Areas of Agreement / Disagreement

Participants express various viewpoints on the causes of the voltage offset and the effectiveness of different models and configurations. There is no consensus on the best approach to resolve the issues presented, and multiple competing views remain regarding circuit design and simulation accuracy.

Contextual Notes

Participants mention potential limitations in the models used and the effects of channel length modulation, which may not be accounted for in all theoretical frameworks. The discussion also highlights the importance of feedback mechanisms in amplifier design.

Who May Find This Useful

This discussion may be useful for electronics students, hobbyists working with differential amplifiers, and professionals interested in circuit simulation and design challenges in LTSpice.