Mitchy190

- 42

- 0

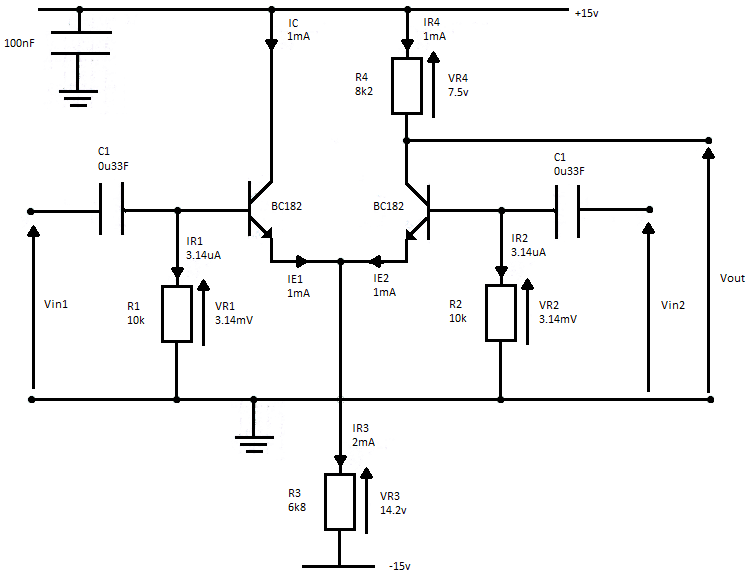

Hey! I was wondering, how would I predict the frequency response of the circuit below when v2 is grounded?

I have actually measured the response which is also shown below, v2 is grounded.

I know the input impedance of the circuit and therefore I calculated the frequency response of the capacitor and input impedance, which form an RC circuit.

This gives the same shape as my measured response which i would expect, but there is an offset, as you can see. I calculated a 'gain' to be around 27-28 which if i were to multiply the transfer function i worked by, the correct offset would occur.

I have no idea what this is, it cannot not be the Gdm or Gcm of the transistor as i have calculated them and not got 27-28?

I got:

Gdm = R4/2*rE = 164, where rE = 25mV/IE = 25mV/1mA

Gcm = R4/2*R3 = 0.603

Please could someone check this out? (:Schematic diagram of circuit, v2 is grounded:

Graphs:

View attachment frequency responses.pdf

I have actually measured the response which is also shown below, v2 is grounded.

I know the input impedance of the circuit and therefore I calculated the frequency response of the capacitor and input impedance, which form an RC circuit.

This gives the same shape as my measured response which i would expect, but there is an offset, as you can see. I calculated a 'gain' to be around 27-28 which if i were to multiply the transfer function i worked by, the correct offset would occur.

I have no idea what this is, it cannot not be the Gdm or Gcm of the transistor as i have calculated them and not got 27-28?

I got:

Gdm = R4/2*rE = 164, where rE = 25mV/IE = 25mV/1mA

Gcm = R4/2*R3 = 0.603

Please could someone check this out? (:Schematic diagram of circuit, v2 is grounded:

Graphs:

View attachment frequency responses.pdf