Kami_Munchkins

- 6

- 0

TL;DR Summary: Hi, i'm trying to talk about the results, this is a research assignment so i have no support

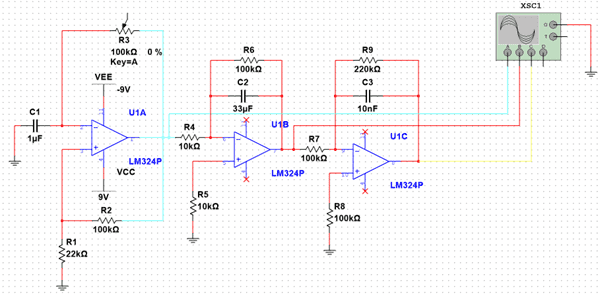

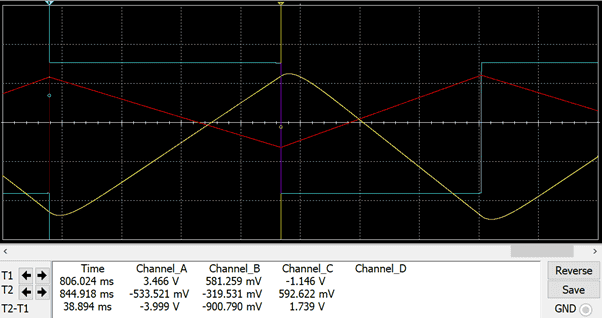

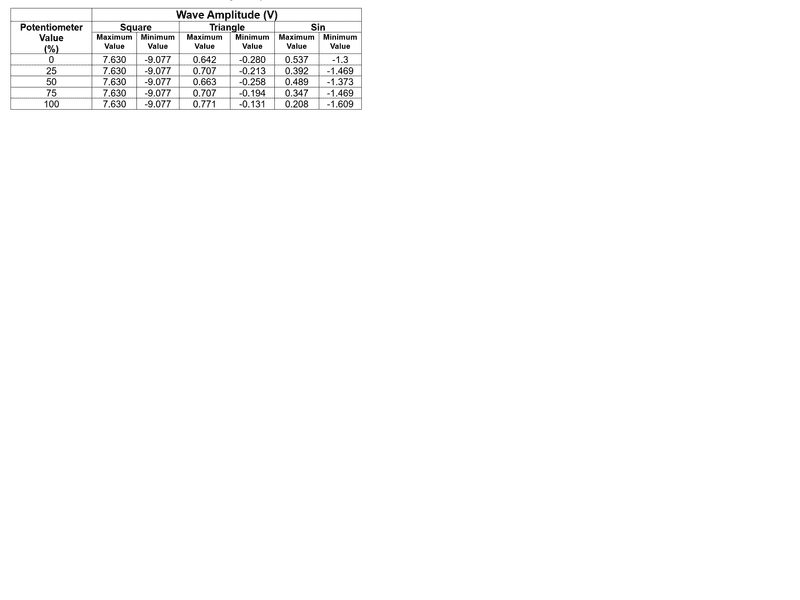

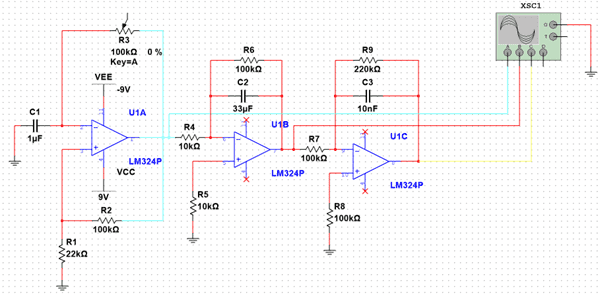

Hello, so here is the circuit. Its a basic signal generator, My issue is in the practical version, the potentiometer effected frequency, but in the simulation this is not the case... I also don't understand why the output voltage for each percentage is going up and down. I assumed since voltage is constant, as the resistance is increased the output should decrease. I can't find any recources either because i don't know what i'm looking for. The table of my results are here too, any help is appreciated.

Hello, so here is the circuit. Its a basic signal generator, My issue is in the practical version, the potentiometer effected frequency, but in the simulation this is not the case... I also don't understand why the output voltage for each percentage is going up and down. I assumed since voltage is constant, as the resistance is increased the output should decrease. I can't find any recources either because i don't know what i'm looking for. The table of my results are here too, any help is appreciated.