timeforplanb

- 16

- 0

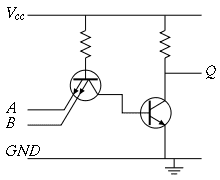

Why do TTL integrated circuits assume unconnected inputs to be at logic level HIGH? Does the answer lie in the circuitry itself or some other factor?

The discussion centers on the behavior of TTL (Transistor-Transistor Logic) integrated circuits regarding unconnected inputs and their assumed logic level. Participants explore the underlying circuitry and logic implications, focusing on how unconnected inputs are treated as logic level HIGH and the effects on output states.

Participants express various viewpoints on the assumptions regarding unconnected inputs, with some agreeing on the logic behind treating them as HIGH, while others seek clarification on the circuitry involved. The discussion remains unresolved regarding the specifics of the internal workings of TTL gates.

Limitations include a lack of consensus on the detailed internal circuitry of TTL gates and the assumptions made about input states. Some participants express uncertainty about the roles of specific components in the circuit diagram.

vk6kro said:

In the diagram, the inputs are only low if current flows out of the device at A or B. Otherwise, they are high.

If either of the inputs is grounded, then the output transistor will not get base current so the output will be high.

Only if both inputs are not grounded, ie high, then the output will be low.

timeforplanb said:I'm not that familiar with the internal circuitry of TTL gates yet. In the diagram, Vcc is one of the inputs right? Where is the other one? Do A and B represent the output terminals?

So, if the input is grounded we know that it goes through a certain circuit so we expect its output voltage to be low? Otherwise, it is high?