Discussion Overview

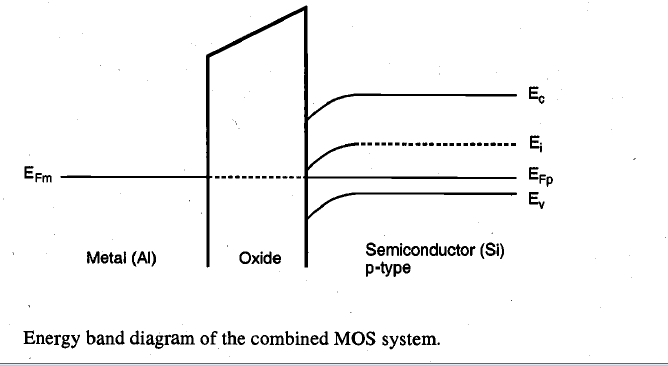

The discussion centers on the behavior of the Fermi level (Efm) in MOSFETs in response to varying gate voltages, particularly focusing on the shifts in energy band diagrams when applying positive or negative gate voltages. Participants explore the implications of these shifts in the context of thermal equilibrium, work function differences, and the concept of flat band voltage (Vfb).

Discussion Character

- Technical explanation

- Conceptual clarification

- Debate/contested

Main Points Raised

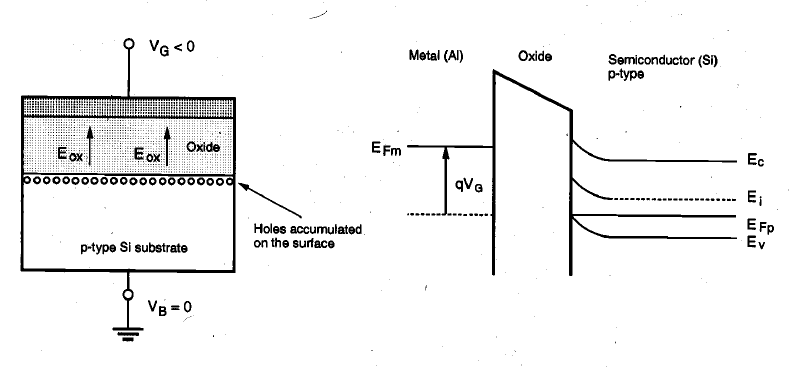

- One participant questions why Efm shifts upwards with negative gate voltage and how it behaves with positive voltage, expressing confusion about the relationship between Efm and Efp.

- Another participant clarifies that the Fermi level is constant only at thermal equilibrium with no external bias, suggesting that shifts occur due to applied voltages.

- A participant references the alignment of Fermi levels in PN junctions, questioning the consistency of Efm and Efp levels in MOSFETs.

- Discussion includes the concept that when no external voltage is applied, Efm and Efp are aligned at the same height, but shifts occur under bias conditions.

- One participant describes the effects of applying positive gate potential, detailing how it attracts electrons and causes shifts in the Fermi levels of both metal and semiconductor, leading to band bending.

- A reference to work function differences is made, explaining that these differences lead to band bending in equilibrium conditions and the significance of flat band voltage (Vfb) in determining further gate voltage effects.

Areas of Agreement / Disagreement

Participants express varying levels of understanding regarding the shifts in Efm and Efp, with some agreeing on the principles of thermal equilibrium and work function differences, while others remain uncertain about the implications of Vfb and its role in the discussion.

Contextual Notes

Participants mention the need for assumptions regarding Vfb and its implications on the behavior of the MOSFET, indicating that the discussion relies on specific definitions and conditions that may not be universally agreed upon.