Discussion Overview

The discussion centers around the operation of voltage multipliers, specifically focusing on why current does not divide between diodes in configurations such as voltage triplers and quadruplers. Participants explore the behavior of diodes and capacitors in these circuits, considering ideal conditions and the implications of impedance and reactance.

Discussion Character

- Technical explanation

- Debate/contested

- Mathematical reasoning

Main Points Raised

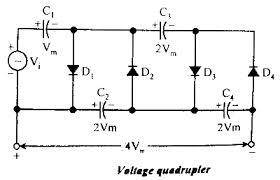

- Some participants question why current does not divide between diodes (D1, D3) or (D2, D4) during the same cycle, suggesting that the charging time is very short.

- One participant proposes that if the diodes are ideal, current flows through C1 and D1 due to lower impedance compared to the alternative path involving more capacitors.

- Another participant describes the function of capacitors in the circuit, explaining how they store energy and interact with the diodes during negative peak pulse voltages.

- There is a correction regarding the classification of the circuit as a negative voltage quadrupler, with some participants asserting it is more than just a doubler, while others express confusion over the output voltage relative to the input waveform type.

- Some participants discuss the implications of using different input specifications (e.g., pulse train vs. sine wave) on the output voltage of the multiplier.

- One participant mentions a simulation demonstrating the output voltage in relation to a sine wave input, noting the output is four times the amplitude.

- Another participant clarifies that the specification of AC voltage as RMS does not change the multiplication behavior of the circuit.

Areas of Agreement / Disagreement

Participants express differing views on the classification of the circuit and its output characteristics, indicating that multiple competing interpretations exist. The discussion remains unresolved regarding the precise nature of the voltage multiplier's output under varying input conditions.

Contextual Notes

Some statements regarding the behavior of diodes and capacitors may depend on assumptions about ideal conditions. The discussion includes unresolved aspects related to the definitions of voltage types and the implications of different input specifications.