gnurf said:

For the sake of the argument the grounds are isolated from each other. In fact, I could've removed the "analog ground" symbol and pretended the right loop was a battery. I have simulated this whole thing with correct models etc and concluded, if only temporarily, that the circuit worked after I tamed the inevitable oscillations with a RC series pair across U3's negative input to output. Does that count as your integrator? The controlling ref voltage V2 is in reality a DC value that changes only slowly e.g. when the user adjusts the current set level.

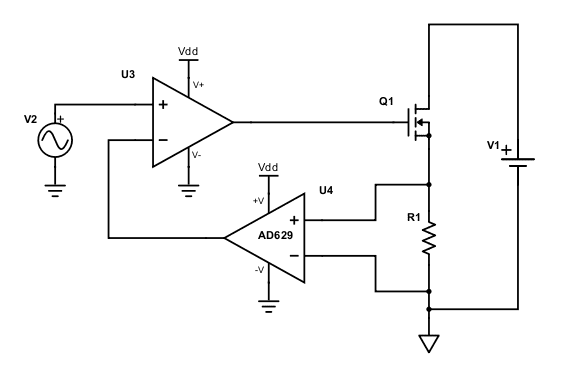

Please see the updated figure below (it's still simplified--I'll shed more light as necessary).

View attachment 247060

I've built a few little loads here and there using basically the same circuit.

As others have mentioned as drawn this won't work, the grounds for the current and error amplifier should be the same ground as the load elements.

The AD629 is a crazy amplifier with +/-270V common mode capability! I assume you chose this part because of the isolation?

I'd do this a little differently:

Putting the isolation barrier inside your control loop makes things needlessly problematic from a stability point of view, so I'd put the opamps on the same ground as the load, and use an isolator (eg opto or what ever) to relay your setpoint signal over the isolation barrier (assuming you must have this isolation). This way you can use normal opamps, something that can go to 15V supply, (a little dual opamp something like LM2904Q1). One to do the current sense amplification, the other to do your error amplifier, strictly speaking of you want to do "true" PI control (assuming you want your steady state error to be zero, you need to integrate) you need to do the K and I separately:

U1 is error amp, U2 integrates, U3 is the proportional gain, U4 is the summation amplifier to bring it all back together.

Depending on how picky you are something like below can often be enough:

I'd also add a small resistive element between the drain and the load input, this makes the power dissipation on the fet(s) a little easier to manage, and reduces the overall gate voltage to current gain, this makes it a little easier to stabilize the whole thing.

Also for me at least, one fet was never enough, its always been at least a kw or so load, so needed quite a few parallel devices, which brings in a whole host of other things to keep in mind, (like source degeneration resistors).