- #1

frenzal_dude

- 77

- 0

If an AND gate is basically two switches in series, and an OR gate is two switches in parallel, how would you physicaly make a NAND/NOT/NOR gate? What is physically going on in the microchip which has these gates?

frenzal_dude said:so that diagram is esentially what makes up computers?

so on any microchip, it has millions of miniature versions of that circuit to make up all other gates/flip flops/registers etc?

frenzal_dude said:so that diagram is esentially what makes up computers?

so on any microchip, it has millions of miniature versions of that circuit to make up all other gates/flip flops/registers etc?

vk6kro said:These functions can be implemented with discrete components, but chips containing four or more gates are available cheaply, so you would probably not bother these days.

However, it is instructive to see how they work:

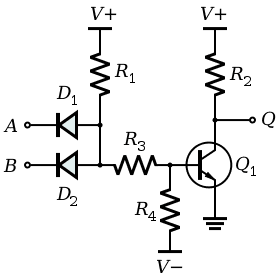

This is a NAND gate. Both inputs (at left) have to be high for the output to be low.

If you reversed both diodes and omitted R1, you would have a NOR gate. If either input was high, the transistor would turn on and the output would be low.

If you removed both diodes and R1, and fed the input to the left of R3, you would have an inverter, or NOT gate.

vk6kro said:"HIGH" and "LOW" depend on the circuit.

In the NAND gate given above, HIGH is something like V+ (maybe 5 to 10 volts) and LOW is something like the saturation voltage of the transistor, so maybe 0.5 volts. This is the voltage across the transistor (from collector to emitter) when it is fully turned on and nearly all the supply voltage is being dropped across the load resistor R2.

In "proper" gates, these terms are strictly defined. So, a "LOW" might be between zero and 1 volt and a "HIGH" might be anything between 4 volts and 5 volts.

This is necessary because these gates have to drive each other and the output of one gate has to be suitable for driving another gate of the same family of logic.

A NAND gate is a type of logic gate that stands for "not and." It is a combination of an AND gate and a NOT gate, and its output is only low (0) when both of its inputs are high (1).

A NAND gate works by using transistors to control the flow of current. When both inputs are high, the transistors are off and the output is low. If either input is low, its respective transistor is on and allows current to flow, making the output high.

To make a NAND gate, you will need two transistors, two resistors, and a power source. The transistors should be of opposite types (e.g. one NPN and one PNP) to ensure proper functionality.

The truth table for a NAND gate is as follows:

| Input A | Input B | Output |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

NAND gates are commonly used in digital circuits and computer processors. They are also used in memory devices, such as flash drives and SSDs, and in electronic devices such as calculators and digital clocks.