PhysicsTruth

- 117

- 18

- Homework Statement

- Given a CE amplifier with gain of about -50, design a buffer emitter follower, mentioning all the parameters that can be controlled by the designer, and connecting the load resistance such that the voltage gain isn't affected.

- Relevant Equations

- ##Z_{in} = \beta (r_{e}+R_{C})##

##A_{v} = -(R_{C}||Z_{in})/r_{e}##

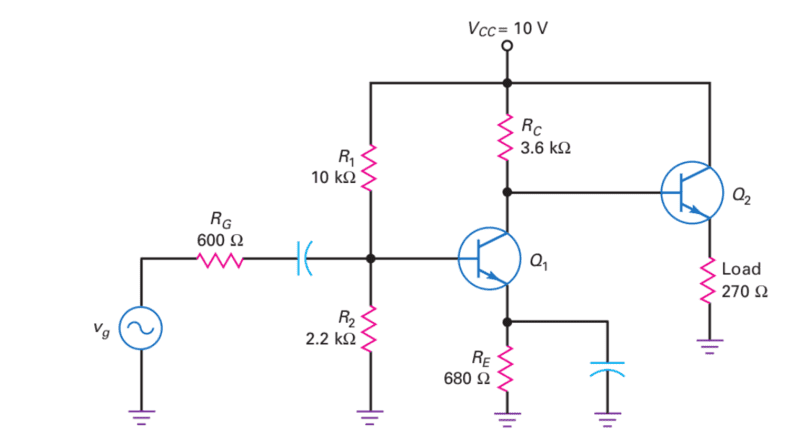

Here is a common CE-CC cascade amplifier-

Here, the output of the emitter amplifier is directly connected to Q2, without any coupling capacitor or any voltage divider bias. This may harm the base-emitter junction of Q2 in case of unwanted output voltage from Q1 collector. But in that case, the calculations would change completely, where ##Z_{in}## would be perhaps ##RB1||RB2||[\beta(r_{e} + R_{C})]##, where r_e would be the internal emitter resistance for Q2 and RB1,RB2 are the base biasing resistors. How to account for the output impedance, the impedance matching and the bias resistor values in this case, such that the AC gain remains at -50?

Here, the output of the emitter amplifier is directly connected to Q2, without any coupling capacitor or any voltage divider bias. This may harm the base-emitter junction of Q2 in case of unwanted output voltage from Q1 collector. But in that case, the calculations would change completely, where ##Z_{in}## would be perhaps ##RB1||RB2||[\beta(r_{e} + R_{C})]##, where r_e would be the internal emitter resistance for Q2 and RB1,RB2 are the base biasing resistors. How to account for the output impedance, the impedance matching and the bias resistor values in this case, such that the AC gain remains at -50?